O 引言

隨著紅外探測技術迅猛的發展,當今紅外實時圖像處理系統所要處理的數據量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA" title="FPGA" target="_blank">FPGA硬件架構進行較為復雜的圖像處理算法運算時,有時就顯得有些捉襟見肘了。使用多信號處理板雖可滿足復雜處理的要求,但系統成本和設計復雜度會大大增加,對于對空間質量有嚴格要求的系統也是不可行的,多處理器系統應用的需求越來越迫切。

本文提出了一種新型的基于FPGA和四端口存儲器的三DSP圖像處理系統。它不同于以往的主從處理器結構,而是3個處理器分別連接四端口存儲器的3個端口,處于同等地位,對圖像數據并行處理,FPGA占用存儲器另一端口進行數據流的控制管理和其他功能實現。這種連接方式增強了系統的重組性和擴展行,軟件開發也更加靈活方便。

1 系統硬件結構

1.1 圖像處理系統的組成

圖像處理系統主要包括DSP及其周邊電路,FPGA電路,四端口存儲器電路、顯示電路、HotLink接口電路等。圖1所示為圖像處理系統的原理框圖。

1.2 FPGA電路設計

FPGA芯片使用Xilinx公司Virtex-4系列的SX35芯片。virtex4系列的FPGA利用90 nm三柵極氧化層技術制造而成,具有百萬門級以上的邏輯資源,大容量片內Block RAM,用于高速數字信號處理的新型XtremeDSP,靈活的數據接口,軟硬件嵌入式處理器核等諸多資源。與前一代器件相比,在其性能和密度加倍的同時功耗卻減半,非常適合用于大規模SoPC系統。配置芯片使用XCF32P芯片。在FPGA外圍連接了D/A視頻芯片,HoTLINK傳輸芯片,SDRAM存儲器等器件,用以完成顯示、存儲等功能。

1.2.1 與HotLink電路接口

HotLink是點對點物理層器件(PHY)的世界領先供應商Cypress導體公司產品,高集成度HotLink收發器是市面上銷售的同類產品中靈活性最強的芯片之一,它提供了很寬的工作范圍(0.2~1.5Gb/s)、可旁路8 B/10 B編碼和備用輸出。每款HotLink獨立通道器件都在一個單片解決方案中集成了發送、接收、先入先出(FIFO)和編碼器/解碼器(ENDEC)功能,為用戶提供了穩定性和通用性最好的高速圖像數據傳輸解決方案。在此選用CY7B923作為發送芯片,將采集到的圖像數據通過HotLink接口發送到圖像記錄設備進行記錄。

1.2.2 擴展存儲器接口

FPGA外接SDRAM做為外擴存儲器。SDRAM芯片選用HY57V561620,該芯片為16位的SDRAM,工作頻率為100 MHz。SDRAM工作狀態轉換圖如下:

1.2.3 與視頻顯示電路接口

顯示電路中選用的數/模轉換芯片為ADI公司的ADV7122芯片,該芯片為三通道10 b的視頻數/模轉換芯片。

1.3 四端口存儲器電路設計

四端口存儲器使用IDT公司的IDT70V5388芯片。該芯片為64K×18 b的同步四端口存儲器,4個端口可同時對存儲器的任何地址進行操作,每個端口的最大輸出速率為200 MHz,因此4個端口總的數據帶寬為14 Gb/s。

存儲器每個端口都設置有郵箱中斷功能,這一功能能夠很好地實現與各個端口相連器件的相互通信。選擇郵箱中斷功能后,每個端口給分配一個郵箱,當某一端口向其他端口的郵箱寫入數據時,該端口將會產生郵箱中斷。PORT1向PORT2的郵箱地址(0xFFFE)進行寫操作,PORT2將產生郵箱中斷,PORT2對該郵箱地址進行讀操作之后清除郵箱中斷。

1.4 DSP電路設計

DSP芯片選用Ti公司的TMS32C6414 EGLZA6E3,其主頻為600 MHz。TMS320C6414是TI公司高性能的定點DSP。該芯片采用超長指令字結構(VLIW),每個時鐘周期可以執行8個32位指令。

2 系統工作流程及軟件設計

系統上電后,DSP1從與其連接的FLASH芯片中讀出非均勻性校正算法所需的系數,傳送給FPGA,FPGA對圖像進行校正,校正結果寫入四端口RAM,圖像拉伸顯示模塊和數字圖像記錄模塊。3個DSP可以從四端口RAM中讀取圖像信息,并行進行圖像處理工作。

2.1 非均勻性較正算法設計

非均勻性是指凝視成像探測器在外界同一均勻光學場輸入時各單元輸出的不一致性。焦平面陣列探測器的非均勻性高達10%~30%,因此焦平面探測器在使用時必須進行非均勻性校正。非均勻性校正算法中,兩點校正算法是最常用的算法,該算法的計算量非常小,校正一個點只需1次加運算和1次乘運算,有利用系統實時實現。

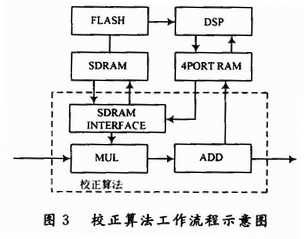

兩點校正公式為:V’=GV+O。其中,V為探測器單元的實際輸出值,V’為校正后的值,G為校正增益,O為校正偏移量值。G和O利用測量兩個不同溫度點的探測器響應計算得出,預先存入FLASH芯片中。系統正常工作時,DSP將系數從FLASH芯片中讀出非均勻性校正算法所需的系數,用乒乓方式寫入四端口RAM中。每寫完1塊數據區后利用四端口RAM的中斷信號通知FPGA將系數讀走,FPGA將得到的系數依次存入SDRAM中。系數傳送完畢后,FPGA開始接收探測器數字圖像信息,同時將校正系數讀出,對原始紅外圖像進行乘加運算。工作流程見圖3。

2.2 圖像拉伸算法設計

圖像拉伸采用自適應直方圖增強算法,表示為如下的映射關系:

式中:yk為增強后圖像的灰度值;Xmax和Xmin為原圖像中像素最大值和最小值;Xk為原圖像的灰度值;a為亮度補償系數,取值為0~1之間,當取0時,即是通常的拉伸算法。

考慮到紅外圖像中可能存在盲元和噪聲,Xmax和Xmin不宜取原圖像中最大最小值。采用分位數法來取圖像中的最大值和最小值可以把盲元和噪聲的影響降到最低,分位數根據盲元和噪聲情況具體確定,一般可取5 %。

圖4給出了直方圖增強算法的FPGA系統框圖,A/D轉換后的14 b數據流進入直方圖統計模塊計算每一像素點的直方圖,根據設定好的分位數計算圖像中像素的最大值和最小值。在每一幀有效數據結束后,根據直方圖統計得到的最大值和最小值,計算灰度映射的除法,這樣每幀只需計算1次除法,而不用對每一像素進行除法計算。之后對得到的因子對每一像素進行乘法及移位計算即可得到直方圖增強算法處理后的圖像數據。增強后的圖像數據通過DAC控制模塊送入電視顯示。

3 結語

針對紅外試試圖像處理系統構建的FPGA+多DSP的硬件平臺,利用FPGA進行調度和時序控制,有效的使3個處理器并行工作,大大提高了系統處理能力。研究并實現了從紅外探測器數據采集到圖像校正、圖像處理,以及圖像顯示的整個流程。系統已應用于工程實踐中,對于空間質量要求苛刻的高性能處理系統有一定的借鑒意義。