對降低地址總線" title="地址總線">地址總線功耗的編碼方法研究與應用正在逐漸增多。本文在簡述地址總線上的功耗來源的基礎上,介紹了幾種典型的地址總線低功耗" title="低功耗">低功耗編碼方法,通過結合實際采用的T0編碼,能有效地降低智能卡芯片" title="智能卡芯片">智能卡芯片的功耗。

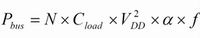

CMOS電路中的功耗來源于兩部分:一部分為靜態功耗,由漏電和其它靜態電流產生;另一部分為動態功耗,由短路電流和負載電容充放電產生。這兩部分中共有三種最主要的消耗:跳變" title="跳變">跳變損耗(switching loss)、短路損耗(short-circuit loss)、漏電損耗(leakage loss)。短路損耗這部分功耗占總功耗的10-15%,而跳變損耗引起的功耗則占到總功耗的70%~80%。N位地址總線的跳變功耗表達式為:

其中,N表示地址總線寬度,Cload表示平均每位地址線的負載,VDD為電源電壓,α表示一個周期內平均電容充放電的次數,f是操作頻率,α×f表示翻轉率。

智能卡芯片內部的地址總線,要將RAM、ROM等模塊相連接,負載比較重,而且地址總線一般走線也比較長,這無疑都將增大地址總線的負載電容。同時,CPU對存儲器訪問頻繁,也增大了地址總線的翻轉頻率。因此,地址總線上消耗的功耗比較大。

低功耗地址編碼方法

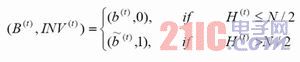

對地址總線進行低功耗設計主要是對其進行低功耗編碼,方法有BI(Bus-Invert)和T0(Zero-Transition)、格雷碼" title="格雷碼">格雷碼、WZE編碼等。它對CPU送出的t時刻與t-1時刻N位地址總線進行比較,總線上變化的位數如果大于N/2,則將總線取反外送,否則就直接外送。地址接收端" title="接收端">接收端收到地址后是否取反根據INV信號線來確定。例如,地址總線為4位,t-1時刻為0000,t時刻為1111,那么將1111取反后送出去。

BI編碼公式如下所示:

式中的b(t)是指t時刻的實際地址,B(t)是編碼后的地址,H(t)是b(t)和b(t.1)相異的位數。

BI解碼公式如下所示:

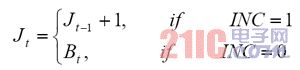

其中,J(t)為解碼后的地址總線。

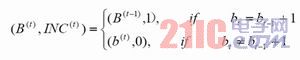

T0碼通過增加一條冗余連線INC來通知地址的接收端總線上的地址是否連續。如果INC為高,表明總線上的地址是連續的,此時所有的地址總線保持不變,地址接收端自動將上一地址加1,作為當前的地址;如果INC為低,表明前后兩次地址并非連續,此時總線將正常地傳送地址碼。

定義b(t)為CPU計算出來的t時刻總線數據(即編碼前的數據),B(t)是t時刻已放到總線上的數據(即編碼后的數據),Jt是解碼器解碼后的數據。則T0編碼的編碼公式為:

與T0編碼相對應的解碼公式為:

將BI和T0兩種方法結合起來,就形成了BI-T0方法。一般而言,地址都是比較連續的,而數據總線則是比較隨機的。BI編碼主要用于數據總線,用于地址總線的時候,一般都帶有緩存。T0編碼具有低延遲和小面積的特性,地址連續的時候,能夠很好地降低地址翻轉次數。在地址連續的時候,使用T0編碼;在地址不連續的時候,使用BI方法,這就形成了BI-T0編碼。

格雷編碼對于連續變化為主的地址總線也是比較有效的。例如,從7變為0,用二進制編碼是由111變為000,要引起跳變3次,而用格雷碼則是由100變為000,只變化一次。對連續數據變換,用格雷碼更簡單有效。

WZE(Working-Zone-Encoding)編碼假設每個瞬間程序只訪問總地址空間的某個工作區(Working-Zone)。地址總線上傳遞工作區的標志和基于工作區基址的地址偏移,該偏移量采用獨熱編碼。WZE主要用于外部地址總線,在它基礎上形成了PBE編碼和擴展WZE編碼。

T0編碼的實現與應用

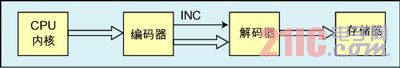

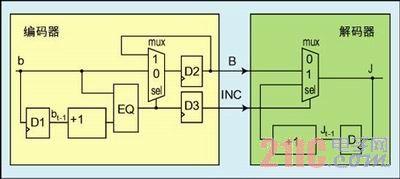

采用T0地址總線編碼的示意圖如圖1所示,編解碼器的結構如圖2所示。b為CPU內核送出來的地址,B為經過編碼器輸出的地址,J為解碼器送往存儲器的地址,INC用來表示地址是否是連續的。編碼器和解碼器的電路規模很小,帶來的額外硬件面積和功耗也很小。

圖1:地址總線編碼示意圖。

圖2:零翻轉編解碼器電路結構圖。

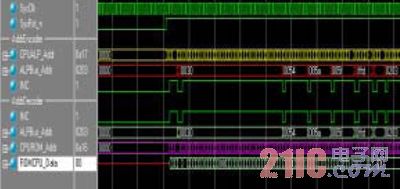

我們選用一個測試激勵,實際運行的波形圖如圖3所示。

圖3:地址零翻轉波形圖。

從圖中可以看到當CPU送出的地址總線是連續的時候,編碼器和解碼器之間的地址總線可以不翻轉,存儲器通過INC信號得到正確的地址。在FPGA仿真的時候,可以將上述激勵的VCD文件輸入XPOWER來分析功耗。使用T0編碼,總功耗為0.467mW,不用T0編碼,總功耗為0.999mW。

本文小結

結合一款8位智能卡芯片的實際情況,對地址總線采用簡單有效的T0編碼,有效地降低地址總線的翻轉次數,從而有助于降低整個智能卡芯片的功耗。