引言

CAN(Controller Area Network,控制器局域網)總線是德國Bosch公司在20世紀80年代初,為了解決現代汽車中眾多的控制與測試儀器之間的數據交換而開發的一種串行數據通信協議。它的短幀數據結構、非破壞性總線性仲裁技術以及靈活的通信方式適應了汽車的實時性和可靠性要求,倍受汽車生產廠商的青睞。隨著汽車電子技術的發展,汽車上的ECU(Electronic Control Unit,電子控制單元)越來越多,如電控燃油噴射系統、防抱死制動系統、防滑控制系統等,相應的數據量也越來越大,如何采用合理的存儲" title="存儲">存儲方案是記錄儀等大容量存儲系統的關鍵。本文詳細闡述了大容量存儲系統系統的整體結構、硬件電路設計。利用“FPGA+單片機”作為存儲控制器,采用基于LZW算法的數據壓縮技術,以SDRAM作為周期存儲和緩存,SD卡作為最終存儲載體。實驗結果表明,該存儲系統可以很好地應用于車載信息記錄儀。

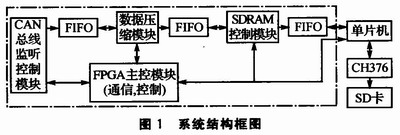

1 系統整體結構設計

如圖1所示,存儲系統主要包括以下模塊:FPGA主控模塊、CAN總線" title="CAN總線">CAN總線監聽控制模塊、數據壓縮模塊、SDRAM控制模塊和單片機控制CH376模塊。本文主要介紹存儲部分,CAN總線監聽控制模塊不做介紹。圖中,點畫線內的部分均由FPGA控制。后端SD卡由MSP430單片機控制,SD協議芯片采用CH376。FPGA控制CAN總線控制芯片、CAN總線收發器" title="收發器">收發器從總線上獲取數據,經過數據壓縮模塊壓縮,存入SDRAM里。這里采用兩種存儲模式:一種是利用SDRAM存儲的可覆蓋性進行周期存儲,具體存儲周期由壓縮率和SDRAM容量決定;另一種是直接存儲,SDRAM作為緩存。當選擇直接存儲時,FPGA與單片機通信,利用FIFO給單片機發送數據,單片機控制CH376將數據存入SD卡(存儲時間由SD卡容量決定)。

2 系統硬件設計

2.1 FPGA主控模塊

FPGA選用Altera公司的Cyclone II" title="Cyclone II">Cyclone II系列芯片EP2C5T14418N" title="EP2C5T14418N">EP2C5T14418N,它具有內部資源豐富、速度快的特點。上電后,主控模塊使能CAN總線監聽控制模塊、數據壓縮模塊、SDRAM控制模塊。如果選擇周期存儲,則不使能單片機;若選擇直接存儲,則讓單片機處于低功耗狀態,當SDRAM有數據時FPGA把數據發給單片機,并使其控制CH376工作。

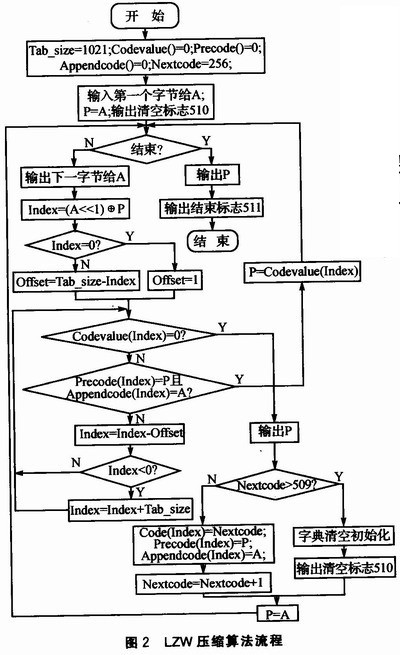

2.2 數據壓縮模塊

壓縮算法采用LZW算法。該算法是一種基于字典的壓縮算法,在數據的壓縮過程中會根據輸入的數據動態地建立一個字典。后續輸入的數據都會在這個字典中進行匹配查找,根據查找是否成功決定壓縮編碼的輸出。該算法的巧妙之處在于,壓縮過程中動態建立的字典不需要與壓縮數據流一道進行傳輸和存儲,然而在對數據進行解壓時也能夠通過壓縮數據流重新建立一個字典,來完成解壓縮。LZW壓縮算法流程如圖2所示。根據該流程,采用C語言設計壓縮與解壓縮軟件以驗證算法和硬件壓縮的正確性,用Verilog語言編寫了壓縮代碼,利用FPGA內部RAM資源建立字典。LZW壓縮算法的硬件邏輯功能框圖如圖3所示。

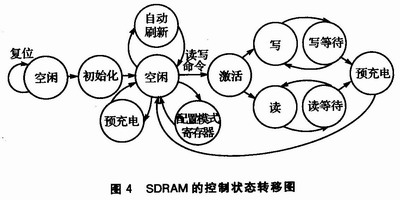

2.3 SDRAM控制模塊

SDRAM(同步動態隨機存儲器)是一種易失性存儲器,以其容量大、價格低的特點得到越來越廣泛的應用。但其控制邏輯復雜,需要周期性刷新操作、行列管理、不同延時和命令序列等。圖4是SDRAM的控制狀態轉移圖。

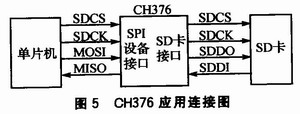

2.4 單片機控制CH376模塊

CH376是一款國產文件管理控制芯片,用于單片機系統讀寫U盤或者SD卡中的文件。CH376內置了SD卡的通信接口、FATl6、FAT32以及FAT l2文件系統等固件,無需自己編寫底層協議,控制簡單,提供2 MB、24MHz的SPI設備接口,支持連接到單片機的SPI串行總線。CH376應用連接圖如圖5所示。

3 系統仿真與測試

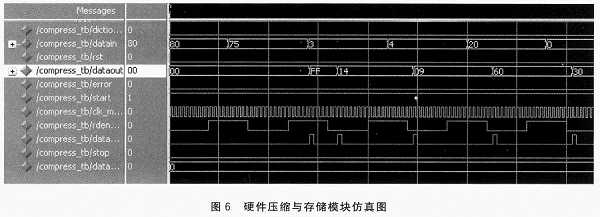

程序編寫完之后,利用Modelsim" title="Modelsim">Modelsim語言仿真軟件對其進行仿真。ModelSim能提供友好的仿真環境,是單內核支持VHDL和Verilog混合仿真的仿真器。它采用直接優化的編譯技術、Tcl/Tk技術和單一內核仿真技術,編譯仿真速度快,編譯的代碼與平臺無關,是FPGA/ASIC設計的首選仿真軟件。硬件壓縮與存儲模塊仿真如圖6所示。仿真結果表明,硬件壓縮與軟件壓縮完全符合。

結語

本文設計了基于“FPGA+單片機”的車載CAN總線采集系統。利用FPGA的優勢編寫了數據壓縮和SDRAM控制兩個模塊,作為存儲系統的核心部分;利用單片機控制能力強、簡單的特點設計了SD卡存儲控制器,作為數據的最終存儲介質,以方便用戶在計算機上直接讀取數據。實驗表明,該系統工作穩定,適合長時間記錄數據。