繼前一個十年的爆炸性增長之后,電信市場正在經歷新一輪整合發展時期,因特網的需求仍在繼續推動產業的創新。目前,家庭視頻和高級商業服務業務的快速發展對全球電信網絡的帶寬提出了更大挑戰。這一挑戰始于網絡接入邊緣,并直接延伸到城域" title="城域">城域網絡和核心網絡。為了響應上述需求,運營商正在追求包括 40Gbps SONET (OC-768 和 OTU3) 以及 40GE 以太網在內的更高的端口速率。越來越多的運營商更是將瞄準了100G" title="100G">100GE端口速率。同時,IEEE 的高速串行 IO 工作組有關 40GE和 100GE ?標準 (IEEE 802.3ba)的制定工作也已經接近尾聲。?

?

商業和經濟的發展形勢迫切地需要可擴展的、靈活的且高效益成本的技術解決方案,從而滿足電信行業不斷變化的需求和標準。為了跟上這些變化,加快超高帶寬系統的部署,有線通信設備生產商正在從傳統的專用集成電路(ASIC)和成品(ASSP)芯片轉向可編程硬件平臺和IP解決方案。 ?

?

向 40GE 和 100GE 的發展?

電信行業最新超高帶寬標準將會影響到整個網絡。這個網絡即要支持目前產生利潤的傳統業務,同時還要滿足運營商為降低運營成本而將核心網絡升級為單個統一的基礎設施的要求。為了保護網絡免受黑客和災難性故障的危害,加密和認證服務也成為強制性的要求。高級流量工程功能則可幫助生產商更高效地實現差異性的高質量端到端服務并更加易于實現收費和贏利。 ?

?

到 2016 年,40GE 和100GE 系統有望達到 42 億美元的年度營收額。對40GE 和 100GE等新的解決方案的最初需求主要來自大型數據和交換中心,但是最新的趨勢表明,文件和存儲虛擬化、高分辨率圖像和視頻等也需要更高速率的接口。[1]?

?

這些需求都對系統和硬件設計人員提出了多方面的挑戰。他們開發的硬件在從

?

可編程技術的經濟效益?

過去幾年時間里,現場可編程門陣列(FPGA)在網絡和電信系統開發中的角色大大擴展,不再是僅僅用于集成電路板上不同元器件之間的橋接" title="橋接">橋接邏輯。隨著 FPGA 的發展推動半導體工藝技術結點從今天的 65nm 轉向 40nm 甚至更小,基于 FPGA 的解決方案既提供了專用芯片解決方案所具有的功能、性能和靈活性,同時又大大降低了開發成本。與 ASSP 相比,對于無法等待成品解決方案而又希望保持競爭力的開發人員來說,FPGA 經常是唯一可選的解決方案。 ?

隨著 FPGA 器件成本不斷降低以及密度和性能不斷提高,今天的 FPGA 已經可以運行整個系統和子系統,適用的最終產品從最低端的 DSLAM 和以太網交換機直到最高端的核心路由器和 WDM 設備。設計人員不僅在系統原型中采用可編程器件,還在量產過程中越來越多地采用 FPGA 器件。這就是有線通信業務能夠繼續成為賽靈思" title="賽靈思">賽靈思 FPGA產品和解決方案最大市場的原因。過去幾年時間里,來自有線通信市場的營收每年約為 6 億美元,約占賽靈思總營業收入的35% 。? ?

?

賽靈思預計2008年其有線通信解決方案的市場產值將超過70億美元,年增長率超過7%。賽靈思大量投資開發參考設計、IP 內核和軟件工具,幫助有線通信系統開發人員將高性能 ?Virtex 和低成本 ?Spartan ?系列 ?FPGA 集成到系統中。賽靈思有線通信解決方案支持范圍廣泛的應用,包括:? ?

?

·????????????? 網絡傳輸市場:?

o???????????? 核心層:? 核心交換機、核心路由器、長途傳輸DWDM?

o???????????? 城域層: 城域交換機、城域路由器、城域DWDM?

o???????????? 邊緣層: 接入/匯接交換機、邊緣路由器、PON(無源光學網絡)、DSLAM、無線回傳?

?

·????????????? 企業網絡市場:?

o???????????? 交換?

o???????????? 安全?

?

適用于

得益于 Virtex-5 系列的模塊化 ASMBL ?架構,賽靈思能夠快速經濟地開發出滿足不同市場發展要求的 FPGA 產品。為幫助開發人員更快地開發

?

Virtex-5 TXT FPGA 包括二款器件,提供豐富的邏輯單元和塊 RAM 組合以及最高密度的高速收發器" title="收發器">收發器。Virtex-5 TXT 器件集成了多達48個 RocketIO 6.5Gbps 多速率收發器(數量達到 Virtex-5 FXT FPGA的2倍),可以提供構建網絡橋接設備所需要的 600Gbps 總帶寬。 由于這些器件基于與其它Virtex-5 FPGA平臺同樣的硬件模塊,因此其中嵌入的收發器已經由賽靈思進行了完全的參數化提取,同時還經過了客戶的現場驗證。??

?

?

Virtex-5 TXT FPGA 平臺? 器件代碼? XC5VTX150T? XC5VTX240T? 邏輯片 (2) ? 23,200? 37,440? 邏輯單元 (3) ? 148,480? 239,616? CLB觸發器? 92,800? 149,760? 最大分布式RAM (Kbits) ? 1,500? 2,400? Block RAM/FIFO w/ECC (36kbits each) ? 228? 324? Total Block RAM (kbits) ? 8,208? 11,664? 數字時鐘管理器 (DCM) ? 12? 12? 鎖相環? 6? 6? 最大單端引腳數 (4) ? 680? 680? DSP48E 邏輯片 ? 80? 96? PCI Express Endpoint 模塊 ? 1? 1? 10/100/1000 Ethernet MAC 模塊 ? 4? 4? RocketIO GTX 高速收發器 ? 40? 48? 封裝 (7,8)? 面積? ?? ?? ?FFA 封裝 (FF): 倒裝片精細間距 BGA ( ?? ?? FF1156? 35 x 360 (40)? ?? FF1759? 42.5 x 680 (40)? 680 (48)?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

100GE MAC 作為系統接口橋接?

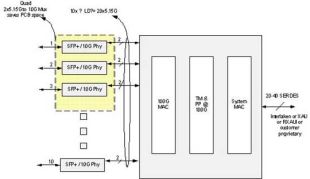

賽靈思公司與電信行業的標準化組織以及其它 IP 和硬件供應商密切合作,提供支持 XAUI、 RXAUI、 Interlaken、 SONET、 ODN 以及其它多個有線標準的解決方案。賽靈思公司與 Sarance Technologies 公司共同推出業界第一個 100GE MAC 解決方案,可以利用 Virtex-5 FPGA 實現全功能 IEEE 802.3ba 的標準。目前,采用了兩片Virtex-5 FXT FPGA、10個外部10Gbps PHY以及眾多系統側接口的該解決方案已經在第1層供應商硬件原型上運行。 ?

?

采用了最新的 Virtex-5 TXT FPGA 平臺的 100GE MAC-to-Interlaken 橋接解決方案在單片FPGA和三個外部多路SERDES 復用器內集成了全部功能,提供了一個風險極低的選擇。 在具體設計中,內建于 GTX 收發器的賽靈思專用 64/66 ?和 ?64/67 編碼/解碼功能節約了近 1/5 的邏輯資源和功耗。 ?

?

?

創新前沿?

新推出的 Virtex-5 TXT FPGA 平臺基于開發人員利用 Virtex-5 器件支持超高帶寬系統的經驗。2006年11月,作為全球第一例 100GbE 傳輸在實際生產網絡上的應用案例,賽靈思 FPGA 器件在由 Finisar 公司、美國 Level3 通信公司、Internet 2 協會以及加州大學圣克魯茲分校 (UCSC)聯合舉辦的 SC06 國際會議上進行展示。Finisar公司與 美國 Level3 通信公司、Internet2 協會 以及加州大學圣克魯茲分校(UCSC)共同合作,成功地在坦帕市(美國佛羅里達州) 和休斯頓市(美國德克薩斯州)之間的約

?

2008年6月,電信巨頭 Comcast 公司宣布利用業界首個100GbE 路由器接口在其現有骨干基礎設施(Philadelphia ?和 ?McLean 之間)上成功完成一項 100GbE 技術測試。該系統同樣的采用了Sarance Technologies 公司運行在 Virtex-5 FXT FPGA 上的高速以太網IP內核 (HSEC) 。目前該內核現在可運行在 Virtex-5 TXT 平臺。?

?

總結?

?

可編程系統解決方案為開發范圍廣泛的有線電信應用提供了一種低成本、低風險的途徑。FPGA構造的性能已經可以支持最高性能達 100Gbps的應用。 做為全球可編程邏輯解決方案領導廠商,賽靈思公司密切關注客戶和市場要求,通過研發硬件器件、軟件和 FPGA IP 在適當的時間提供適當的解決方案,為有線電信行業向 100GE 邁進提供所需要的規模經濟效應和靈活性,同時幫助提供服務提供的質量。 ?

?

有關賽靈思有線電信市場解決方案的更多信息,請訪問: http://www.xilinx.com/cn/esp/wired.htm。?

[1] Lightwave, April 2008, http://lw.pennnet.com/display_article/325344/13/ARTCL/none/none/1/40/100?

?

[2] Lightwave, January 2007, http://lw.pennnet.com/display_article/281527/13/ARTCL/none/none/1/Indust?

?