?? 在Honolulu舉辦的2008SymposiumonVLSITechnology技術論壇上,IntelCorp.的研究人員發布了新一代基于絕緣硅(SOI)通過埋層氧化層(BOX)儲存電荷的浮體存儲器單元(FBC)。針對一些專家提出的縮小尺寸將導致器件的荷電保持能力下降的疑慮,研究人員指出FBC技術能夠有效地改善上述問題,這項技術可能在16nm技術節點時切入市場,并能夠向下延伸至10nm" title="10nm">10nm節點。

?

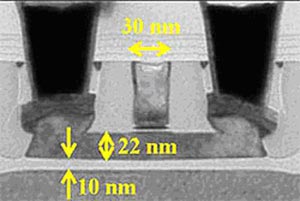

?? Intel器件研發部主管MikeMayberry介紹道,相對于其它使用較厚的埋層氧化層的FBC產品而言,Intel的研發團隊使用10nm的BOX并在其上方覆蓋22nm" title="22nm">22nm的硅材料" title="硅材料">硅材料。這項技術在速度上還不能與傳統的SRAM相提并論,但是FBC結構比目前廣為使用的6晶體管(6T)的SRAM具有更小的單元面積。

?

?? Intel研發的浮體存儲器單元(FBC),器件的柵電極為32nm" title="32nm">32nm并使用10nm的埋層氧化層(BOX)儲存電荷。

?

??? “如果我們能夠使FBC滿足使用的需求,單一晶體管結構無疑比6T內存更具有優勢,”Mayberry說道。

????

??? Mayberry介紹道,FBC內存結構不再需要獨立、制造成本高昂的電容結構,而是將電容與單元本體相互結合。通過這種方式,FBC結構能夠在單元面積上具備更大的儲存容量。這能夠進一步提高運算速度并大為降低制造成本。此外,Mayberry還指出,采用較薄的BOX以及硅材料的FBC結構在低電壓條件下的表現與厚SOI單元相當。Intel展示的30nm柵電極(Lg)的FBC結構,其單元面積約為0.01μm2。

?

??? Intel的研究人員采用本公司的45nm" title="45nm">45nm邏輯技術平臺進行流片試驗,在提高源/漏摻雜和取消井摻雜的平面結構上分別對比先柵極、后柵極制造工藝對這項技術的影響。具體內容參見,《AScaledFloatingBodyCellMemorywithHigh-k+MetalGateonThin-SiliconandThin-BOXfor15nmNodeandBeyond》,作者:Intel技術生產制造部(TMG)Hillsboro,Ore.以及IbrahimBan,UygarAvci,DavidKencke和PeterChang。

?

??? 研究人員公布了柵長為60nm的FBC器件性能,基于數據可知FBC結構具有良好的晶體管電學性能,較穩定的閾值電壓(Vt)以及優異的內存表現。上述結果參見《functional 32n mgate length silicon suggests the feasibility of this technology at the 11n mnode》,文中柵長為32nm的器件是迄今為止發布的最小尺寸的器件結構。文中指出:“在>100ms的前提下,儲存數據是穩定的,FBC結構能夠適用于32nm柵長的器件并可以進一步向前發展。”

?

??? 當邁入16nm節點時,FBC的單元尺寸將比6TSRAM更小。采用40nm柵電極、60nm柵電極間隔以及60nm金屬導線的設計規則,折疊型位線結構的FBC單元面積是0.012μm2,而開放型位線結構的將達到0.006μm2。

?

??? Intel的成果為FBC內存領域的研究注入了新的活力。此前,IBM的研究人員提出隨著器件尺寸的縮小很難確保存在BOX中的電荷不會流失。

?

??? 去年晚些時候,InnovativeSiliconInc.(ISI,Lausanne,Switzerland)對外發布了第二代Z-RAM設計結構。作為FBC領域的先驅,ISI已經將其知識產權轉讓給了AdvancedMicroDevicesInc.(AMD,Sunnyvale,Calif.)、HynixSemiconductorInc.(Icheon,Korea)以及其它一些知名半導體企業。此外,在日本ToshibaCorp.(Tokyo)和RenesasTechnologyCorp.(Tokyo)也在積極研究FBC技術。???

?

??? “FBC單元可以用于高速緩沖存儲器,面積上會比目前在45nm技術節點使用的6TSRAM縮小30%”,Mayberry說道。而且這項技術能夠進一步向下延伸,滿足16nm乃至更為先進技術的需求。最后,他透露Intel在FBC方面的研究比目前業界公布的技術先進兩代以上。