傳統的寬帶陣列接收機用多臺單通道接收機并行工作,并行的同時接收不同頻點上的信號來達到全頻域覆蓋的目的,也可以用多通道接收機多個通道并行同步的工作來實現,前者增加了系統成本和讓整個并行系統同步工作的復雜度,后者當信道數比較大和指標要求比較高時,信號處理的復雜度和器件實現的可行性要求很高。基于多相濾波的數字信道化陣列接收機在通信類電子戰中對跳頻信號的快速搜索以及雷達對抗中對捷變頻雷達信號的全概率截獲等表現出很高的潛在研究和應用價值。

1 系統組成

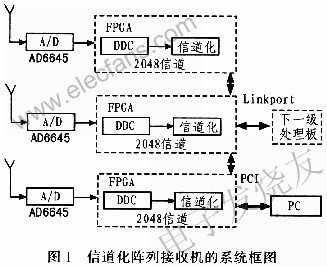

該系統設計是基于多相濾波的信道化原理,對寬帶陣列接收機進行設計,實現在單板上同時處理3路中頻70 MHz,帶寬30 MHz的模擬信號,其中子信道帶寬僅25 kHz,有利于后端模塊進行精細化信號分選和處理,信道化多相因子為8。帶外抑制大于55 dB。系統還可以將陣列中某一路子信道數據通過PCI接口上傳到PC機顯示信道化結果。系統具有完善的時鐘方案,多板連接時,可達到陣列天線的同步要求。另外,由于系統大部分數字信號處理都是在FPGA中完成,所以整個系統具有功耗小、體積小、成本低、操作靈活的特點。圖l為信道化陣列接收機的系統框圖。

2 硬件電路設計

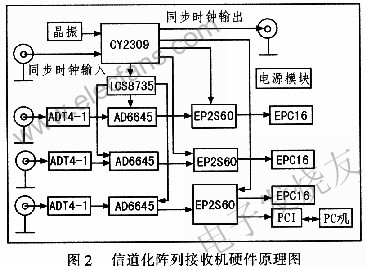

該中頻數字接收機的硬件設計原理圖如圖2所示。中頻信號經過單端轉差分電路以差分信號形式輸入到模數轉換器,AD*5將模擬信號轉換成數字信號送入FPGA中進行處理,其中一片的處理結果通過PCI上傳到PC機顯示,兩片時鐘分配器件分別提供系統需要的多路單端和差分時鐘。

2.1 系統時鐘設計

系統的時鐘由一個晶振產生,也可以由外部提供。本系統采用102.4 MHz的晶振。晶振需要同時給FPGA和AD*5提供時鐘,為了防止其驅動力不足,設計中采用了CYPRESS公司的高速時鐘分配器件CY2309,而AD*5的時鐘輸入為差分(LVPECL)形式,倍頻器件ICS8735可以提供LVPECL電平的差分信號。所以晶振輸出的102.4 MHz時鐘首先通過時鐘分配器件CY2309將其分為5路,每路均與輸入相同,其中3路直接提供給3片FPGA,一路接到時鐘輸出接口,供下級板子使用,一路經過驅動器件ICS8375轉為3路差分時鐘提供給3片AD*5作為采樣時鐘。由于CY 2309和ICS8375都是零延遲器件,這樣可以使多板之間保持時鐘同步,減小因延遲帶來的誤差。

2.2 AD采樣電路設計

本系統采用的模數轉換器是AD*5(14位),其最高采樣率為105 MS/s,在中頻為70 MHz時的SNR是73.5 dB,SFDR是89 dBc,模擬帶寬高達200 MHz。

AD采樣率為102.4 MS/s,采樣時鐘要求質量高且相位噪聲低,如果時鐘信號抖動較大,信噪比容易惡化,很難保證有效采樣位數的精度。在布線時,應保證從晶振到時鐘輸入腳距離盡量短并且在其周圍用地包圍起來,提供充分的最短回流路徑,采樣電路與其他數字電路盡量隔離。模數混合電路設計時采用了分區不分割的方案,以提高系統的電磁兼容性。在整個采樣電路下應大面積敷銅接地,以降低可能受到的電磁干擾,同時也可降低對其他電路的干擾。為了優化性能,時鐘信號采用差分形式供給,要求交流耦合。

2.3 FPGA部分設計

FPCA器件選用了Altera公司StratixⅡ系列的EP2S60。StratixⅡ器件采用基于1.2V、90 nm的先進的SRAM工業制造,功耗低。EP2S60F6 72有48 352個ALUT,等價LE*40個,2 544 192 bit RAM,18x18的乘法器144個,12個PLL。

FPGA配置器件選擇的是EPC16,采用同步并行配置方式(FPP)加載FPGA,用JTAG的方式可以給級聯的3片FPGA依次加載程序,也可以給EPC-I6加載程序。

3 FPGA內部信道化模塊實現

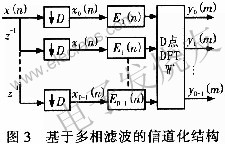

基于多相濾波的信道化模塊是本系統的重點。根據文獻,多相濾波信道化結構如圖3所示。

圖3中分支上的信號xk(n)與輸入信號x(n),以及分支濾波器Ek(n)與原型低通濾波器h0(n)之間的關系為:xk(n)=x(nD-k),Ek(n)=h0(nD+k)k=0,1,…,D-1。所以,進入分支上的數據與分支濾波器系數各是輸入信號和原型低通濾波器系數的延時抽取得來。分支濾波器的長度定義為多相因子,本系統的多相因子為8。

多相濾波的原型低通濾波器由MATLAB產生,采用函數REMEZ優化FIR濾波器估計算法,這里設計出來的濾波器通帶截止頻率為12.5 kHz,過渡帶寬為11 kHz,阻帶衰減為一100 dB。階數為16 383階。

圖3所示的基于多相濾波器組的高效信道化結構,具有以下幾個優點:1)各個支路共用一個低通FIR濾波器,減小FPGA用于存儲系數的RAM資源;2)DFT可以用快速傅里葉變換FFT實現,提高計算效率;3)由于采用多相濾波結構,計算量上極大地減少,可實現性增強。這些優點為信道化結構的工程實現提供很好途徑。

4 測試結果

系統輸入測試信號為單頻正弦信號,VPP為1 V,信號經過AD采樣,DDC,信道化后,數據結果經過PCI上傳給PC機作分析和顯示。

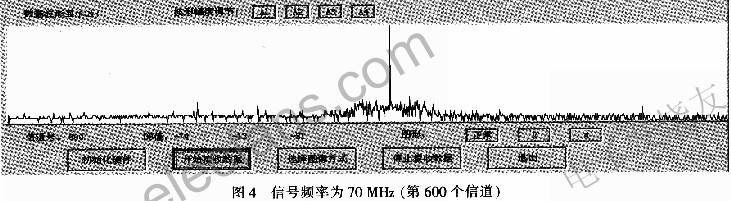

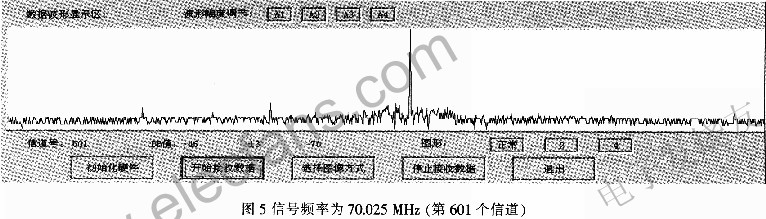

用Microsoft Visual C++6.0制作的界面中:橫坐標是信道號,縱坐標是歸一化功率值(dB),以數據形式顯示的內容有:信號功率最大值對應的信道號、子信道輸出相對于輸入幅度的dB值以及相鄰的兩個信道的dB值。如圖4和圖5所示,輸入信號頻率分別為70 MHz,70.025 MHz,經過信道化后,在對應的信道號上都能輸出譜線,頻率分辨率達到25 kHz。經過多次重復測試,系統對相鄰信道的帶外抑制都達到55 dB以上。

5 結論

該系統主要器件包括AD*5、EP2S60,其中AD6*實現ADC,EP2S60負責系統控制、通信、算法實現,最終來實現了信道化接收功能。因此,該系統具有高度的靈活性和很強的通用性,可通過軟件的重載或升級完成不同指標要求、不同模式的系統結構。在多板連接時,可以構成一個更大的陣列系統,可以用于DOA和DBF。