1 引 言

現場可編程門陣列(FPGA)用硬件電路完成算法的過程,一方面解決了系統的開銷問題,提供了提高系統整體性能的條件,另一方面,由于靜態RAM型的FPGA具備可重構特性,這使得資源利用率得到顯著提高。FPGA既具有通用計算系統的靈活性,又有專用處理系統的性能,對實現高性能信號處理具有很高的應用價值,而且可重構的特性使其可以根據算法來調整相應的通信結構和數據字長。FPGA以其高度的靈活性與硬件的高密度性在通信信號處理中得到了廣泛的應用。

在對Xilinx公司的Virtex-E系列FPGA芯片進行充分理解的基礎上,結合炮兵某數字測距定位系統的實現,這里設計了偽碼的測距電路,并對其FPGA的實現進行了分析。

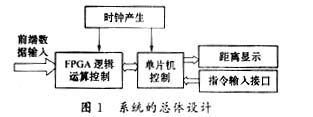

系統偽碼測距電路總體設計如圖1所示。

系統根據前端輸入數據進行碼的捕獲與跟蹤,這些都在FPGA邏輯運算控制部分實現。該部分是系統的核心。

單片機控制部分主要實現數據的計算以及人機的信息互換。該部分對輸入數據進行運算,以得出距離信號;并負責將距離信號進行顯示,同時還可根據外部指令控制系統的工作。指令輸入接口可以控制數據顯示的刷新頻率,控制系統的工

作進程。

時鐘產生部分的主要功能是為單片機控制部分及FPGA邏輯運算控制部分產生所需的不同的時鐘信號。

2 偽碼測距原理

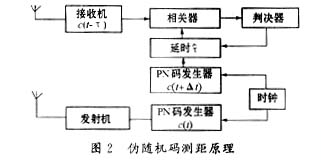

系統采用轉發式二次偽隨機碼測距,即主控站發射的隨機測距信號經用戶站轉發后再與本地碼進行相關運算,通過測量兩者相關峰的位置來確定信號到達的時間,根據收發之間的時間差即可確定主控站與用戶站之間的距離,如圖2所示。

PN碼的相關特性取決于所取碼的類型和長度。分析表明,當接收到的PN碼與本地碼相差一個碼元以上時,二者的相關值接近于最大輸出的1/p(p為偽碼周期中的碼元數,即碼長);當時間相差為零,即兩序列完全對準時,輸出最大;當二者的時間差為正負一個碼元之內時,相關值隨著時間差的變化而變化。在一個序列周期內,相關值只在一個碼元寬度內有明顯變化,為三角形,其它時間基本為零。圖3為一個m序列偽碼的自相關函數的示意圖。

相關峰可以被用來測量兩個PN序列之間的時間差,借此測量用戶站與主控站之間的距離。利用三角形相關峰的線性斜邊,粗同步到一個碼片寬度內之后,通過PN碼跟蹤環可實現碼片內的精同步。

3 偽碼同步模塊實現

擴頻碼的同步又分粗略同步和精確同步,也就是擴頻碼的捕獲和跟蹤。通過擴頻碼的捕獲可以使本地偽碼與接收到的碼元基本保持同步,獲得二分之一碼元寬的同步精度。但由于發射機和接收機的相對運動及時鐘的不穩定,特別是測距的需要,必須對接收信號進一步跟蹤,使本地參考信號盡可能跟隨接收信號的變化。擴頻碼的跟蹤可以使同步精度控制在更小碼元周期范圍內,由此得到的距離估計誤差較小。

常用的偽碼捕獲方法有并行捕獲方法和串行捕獲方法。并行捕獲法的捕獲時間短,但對長的PN碼,匹配濾波器設備量大,實現困難;對擴頻碼捕獲使本地碼與接收碼的相位保持二分之一碼元的同步精度,工程上多采用滑動捕獲法,使接收到的序列與本地產生的序列進行滑動比較,直至滿足要求。經綜合比較,采用在實現上較簡單的簡單逐步移位串行捕獲法。

偽碼跟蹤即使本地參考信號盡可能跟隨接收信號的變化,擴頻碼的跟蹤可以使同步精度控制在十分之一碼元周期范圍內,以減小距離估計誤差。擴頻碼的跟蹤通過碼跟蹤回路實現。延時鎖定環DLL和抖動環TDL是碼跟蹤環的兩種配置,TDL和DLL都可用于相關模式和非相關模式。TDL可以克服DLL的增益不平衡問題,但會導致3dB的跟蹤誤差而使性能降低,一般采用非相干延時鎖定環DLL。

在本原理性設備的研制過程中,不加任何導航數據,經數字下變頻后所得的數信號理論上是相對發射具有一定延時的PN序列。圖4給出了偽碼捕獲與跟蹤的實現過程。碼跟蹤采用的是超前-滯后型數字鎖相環(LL-DPLL),鑒相器逐周地比較輸入信號與本地參考信號的相位,根據相位超前或滯后相應地輸出一個超前或滯后脈沖,雙相高頻時鐘源產生兩路反相的高頻時鐘。同時,控制電路根據鑒相電路的超前或滯后脈沖控制分頻器輸入脈沖的加減,以達到調整本地PN碼相位的目的,實現精同步。只要根據記錄下的超前與滯后脈沖的數目(一個碼片內的延時),以及捕獲時記錄下的數據(一個偽碼周期內的延時)即可計算出傳輸延時。

4 工作流程

4.1 碼的捕獲

在本地產生與發送碼完全相同并有一定相對時延的本地碼,將本地碼與接收到的PN碼進行逐位比較,相同則計數器加1,即記錄下相同的碼片數。持續一個PN碼周期后,將二者相同的數目與門限進行比較,如果大于門限則判斷為已經捕獲到PN碼,輸出同步標志信號;否則,通過控制電路扣除PN碼的產生時鐘一個脈沖,使PN碼延遲一個碼元,并將計數器清零,同時另一計數器記錄下PN碼延遲的碼元數,并最終輸出粗同步輸出信號。

4.2 精同步

中頻數字化處理后的信號與本地PN碼時鐘信號進行鑒相比較,輸出超前或滯后脈沖信號,根據超前與滯后信號,加上或減去一個高頻脈沖,從而控制分頻器的輸入,達到調整本地時鐘相位的目的。同時記錄下加減脈沖的數目,計數器的輸出即為精同步輸出信號。二者達到同步時,也即完成精同步時,鑒相器產生交替的加減脈沖。

4.3 測距

當同步標志信號輸出為真時,根據精同步輸出信號與粗同步輸出信號即可以計算出傳輸的延時,得到測量距離。

5 結束語

按圖4所示結構用FPGA實現偽碼的同步,還應綜合考慮芯片內部資源利用情況與綜合后的運行速率問題。設計時利用VHDL(Very High SpeedIntegrated Circuit Hardware DescriptionLanguage)硬件描述語言進行設計。VHDL語言描述能力強,覆蓋面廣,抽象能力強,可讀性好。運用VHDL語言可以大大減輕設計工作強度,提高設計質量,降低出錯率。

根據初步的試驗結果,PN碼碼長為127,速率為4MHz時,最大捕獲時間約

為幾個ms。采用高頻時鐘,精同步可達到十分之一碼元的分辨率。

參考文獻

1 常 青.可編程專用集成電路及其應用與設計實踐.北京:國防工業出版社,1997

2 查光明等.擴頻通信.西安:西安電子科技大學出版,1990