摘? 要: 介紹了一種基于FPGA和DDS(Direct Digital Synthesizer)技術(shù)的跳頻" title="跳頻">跳頻信號源實現(xiàn)方案。DDS采用AD公司的最新頻率合成" title="頻率合成">頻率合成器件AD9852,其中頻率控制字" title="控制字">控制字存儲在FPGA內(nèi)部RAM單元中, FPGA通過40針總線接口向AD9852寫入頻率控制字。該信號源具有可編程、可升級的優(yōu)點。

關(guān)鍵詞: DDS? FPGA? 頻率合成器" title="頻率合成器">頻率合成器? 跳頻通信

?

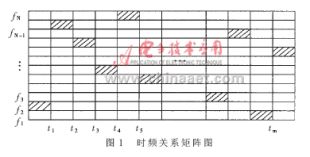

在眾多的通信技術(shù)中,擴頻通信技術(shù)由于具有獨特的抗干擾能力以及寬的使用頻帶而在軍事通信領(lǐng)域倍受青睞。根據(jù)擴頻通信調(diào)制方式的不同,它可以分為直接序列擴頻方式(DS)、跳頻方式(FH)、跳時方式(FT)及兼有以上方式中二種以上的混合方式。其中跳頻通信具有保密性好、不易受遠近干擾和多徑干擾的影響等優(yōu)點,是一種很有前景的通信方式。跳頻系統(tǒng)的頻率跳變" title="跳變">跳變,受到偽隨機碼的控制。不同的時間、不同的偽碼相位,頻率合成器產(chǎn)生的相應(yīng)頻率也不同。把跳頻系統(tǒng)的頻率跳變規(guī)律稱為跳頻圖案。跳頻圖案是時間和頻率的函數(shù),故又稱為時間-頻率矩陣,簡稱時頻矩陣。時頻矩陣可直觀描述出頻率跳變規(guī)律,如圖1所示。

?

?

跳頻圖案的設(shè)計是跳頻通信系統(tǒng)的一個關(guān)鍵問題,直接影響到跳頻系統(tǒng)的保密、抗干擾、多址等性能。一般要求跳頻圖案的周期要長,這就要求控制跳頻圖案的偽隨機碼周期要長,即移位寄存器的級數(shù)要大。

1 基于FPGA和DDS技術(shù)的跳頻信號源設(shè)計

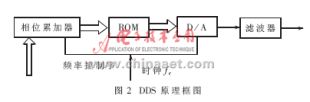

跳頻信號源即為載波頻率按照一定跳頻圖案跳變的信號發(fā)生器。設(shè)計一個性能優(yōu)異的跳頻信號源,困難在于其優(yōu)良的頻譜性能。筆者提出了一種基于FPGA[1][2]和DDS技術(shù)的跳頻圖案的設(shè)計方案。指標如下:600跳/秒跳速;20個跳頻點;3.4MHz跳頻基帶;68MHz跳頻帶寬;106.78MHz~172.14MHz跳頻頻率中20個頻點。DDS采用AD公司的最新頻率合成器件AD9852,寫頻率控制字采用ALTARA公司的可編程邏輯器件APEX20K系列中的EP20K100,其邏輯資源為10萬門,兩者通過40針總線接口相連[3]。其中,FPGA完成存儲頻率控制字、定時寫入頻率控制字的功能,AD9852則實現(xiàn)頻率合成輸出。頻率合成器DDS是跳頻信號源中的一個關(guān)鍵部件,其原理如圖2所示。這種頻率合成器工作頻率高,可達GHz數(shù)量級;分辨率高,可達1Hz以下,穩(wěn)定度高;體積小,重量輕,集成度高,這些都是其他頻率合成器件難以比擬的。AD9852是近年推出的高速芯片,具有小型的80管腳表貼封裝形式,其時鐘頻率為300MHz,并帶有兩個12位高速正交D/A轉(zhuǎn)換器、兩個48位可編程頻率寄存器、兩個14位可編程相位移位寄存器、12位幅度調(diào)制器和可編程的波形開關(guān)鍵功能,并有單路FSK和BPSK數(shù)據(jù)接口,易產(chǎn)生單路線性或非線性調(diào)頻信號。當采用標準時鐘源時,AD9852可產(chǎn)生高穩(wěn)定的頻率、相位、幅度可編程的正、余弦輸出,可用作捷變頻本地振蕩器和各種波形產(chǎn)生器。AD9852提供了48位的頻率分辨率,相位量化到14位,保證了極高頻率分辨率和相位分辯率,極好的動態(tài)性能。其頻率轉(zhuǎn)換速度可達每秒100×106個頻率點。在高速時鐘產(chǎn)生器應(yīng)用中,可采用外接300MHz時鐘或外接低頻時鐘倍頻兩種方式,給電路板帶來了極大的方便,同時也避免了采用高頻時鐘帶來的問題。在AD9852芯片內(nèi)部時鐘輸入端有4~20倍可編程參考時鐘鎖相倍頻電路,外部只需輸入一低頻參考時鐘60MHz,通過AD9852芯片內(nèi)部的倍頻即可獲得300MHz內(nèi)部時鐘。300MHz的外部時鐘也可以采用單端或差分輸入方式直接作為時鐘源。AD9852采用+3.3V供電,降低了器件的功耗。工作溫度范圍在-40°C~+85°C。

?

本文采用AD9852所設(shè)計的頻率合成器結(jié)構(gòu)如圖3所示。DDS模塊分成二路輸出:(1)第一路輸出100MHz~150MHz信號;(2)第二路輸出150MHz~200MHz信號。其中DDS輸出12.5MHz~25MHz的信號,經(jīng)SWCON開關(guān)分成兩路輸出,一路輸出12.5MHz~18.75MHz信號,經(jīng)放大倍頻、濾波,輸出100MHz~150MHz信號;另一路輸出18.75MHz~25MHz的信號,經(jīng)放大倍頻、濾波,輸出150MHz~200MHz 信號。

?

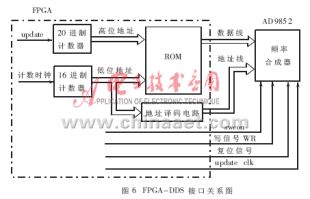

2 FPGA與DDS接口設(shè)計

FPGA主要完成從外部向DDS寫入頻率控制字功能,其中頻率控制字存儲在FPGA內(nèi)部RAM單元中。雙方通過40針總線連接,其中信號線為:8位數(shù)據(jù)線、6位地址線、復位信號、update clk(頻率跳變信號)、swcon(開關(guān):高頻段和低頻段轉(zhuǎn)換信號,當swcon為低時輸出高頻段,當swcon為高時,輸出低頻段)、wr(寫信號)。

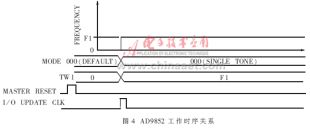

AD9852用于頻率合成時工作在單頻模式(single tone mode),其工作時序關(guān)系如圖4所示。

?

?

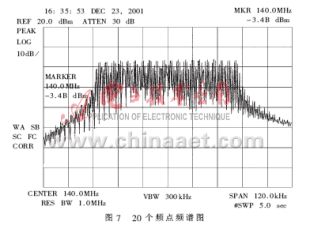

由圖4可以看出,首先必須對AD9852復位。復位信號為高有效,然后寫入頻率控制字,當update clk有效時,即有頻率F1輸出。其中AD9852寫入頻率控制字分為并行寫入和串行寫入兩種模式,本文采用FPGA并行寫入方式。AD9852并行寫入頻率控制字時序關(guān)系如圖5所示。基于以上AD9852的工作時序關(guān)系,設(shè)計的FPGA-DDS接口如圖6所示。發(fā)射FPGA采用一塊ALTERA公司的APEX20K100系列芯片,該芯片邏輯單元為4160個,最大RAM容量為53,248bit,完全能夠滿足生成跳頻圖案的要求。圖6中update為AD9852頻率字更新信號,根據(jù)指標要求按1/600s更新一次頻率。圖6中20進制計數(shù)器對update信號進行20進制計數(shù)。每計數(shù)一次,16進制計數(shù)器控制ROM的低位地址輸出一組頻率控制字,由AD9852合成一個頻率;當計滿20次時,則依次輸出20個頻點。20組頻率控制字依次存放在FPGA內(nèi)部RAM單元內(nèi),由外部地址信號驅(qū)動其按順序輸出。若要改變跳頻圖案,只需改變20組頻率控制字存放順序,或者改變外部地址信號驅(qū)動順序即可。采用頻譜儀觀察結(jié)果如圖7所示。由圖7可以看出,頻譜均勻分布在100MHz~170MHz之間,各項指標均達到預期要求。

?

?

?

本文討論了一種基于FPGA及DDS技術(shù)設(shè)計的跳頻信號源。從實驗結(jié)果可以看出,各頻點具有純凈的頻譜結(jié)構(gòu)、等間隔的跳頻帶寬。樣機測試結(jié)果證明所設(shè)計的信號源完全滿足指標要求。

?

參考文獻

1 趙雅興. FPGA原理、設(shè)計與應(yīng)用. 天津:天津大學出版社, 1999

2 侯伯廷,顧新編. VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計.西安:西安電子科技大學出版社,1999

3 CMOS 300 MSPS? Quadrature Complete-DDS AD9852?ANALOG DEVICE Cor., 2000