摘 要: 介紹了USB設備控制器" title="設備控制器">設備控制器的基本功能和原理,提出了一款基于6502MCU的通用的帶HUB的全速USB設備控制器的體系結構,并完成了整個芯片的設計,而且通過了FPGA驗證。這款芯片可以用來開發帶HUB的全速USB設備、全速USB設備或全速USB HUB。

關鍵詞: USB HUB SIE 轉發器 FPGA

近年來,USB技術已經成為計算機領域發展最快的技術之一,得到了廣泛的應用。早在1998年,由于USB1.1規范的推出以及Windows98加強了對USB的支持,USB就得到了飛速的發展和普及,各種USB設備不斷涌現。2000年,USB2.0規范推出之后,USB一改只能適用于中低速設備的局面,在高速傳輸領域也占領了大量的市場份額。2001年推出的USB-OTG解決了大量USB設備之間的直接互連問題,因此USB規范將得到更加迅速的發展。

根據USB規范,USB系統的拓撲結構呈金字塔狀,集線器(HUB)是金字塔中不可或缺的部件,是主機與設備之間建立連接的橋梁。根據USB2.0規范,全速USB HUB可以連接低速、全速和高速下行設備(高速設備降為全速運行)。

本文提出一款基于6502 MCU的通用的帶HUB的全速USB設備控制器的體系結構,并完成整個芯片的設計。這款芯片可以用來開發帶HUB的全速USB設備、全速USB設備和全速USB HUB。

1 系統設計

常見的USB設備控制器的功能結構框圖如圖1所示。收發器" title="收發器">收發器用于實現物理層的USB規范,它包含一個接收器和一個發送器,接收器用于接收和判決總線D+、D-的信號,發送器用于驅動D+、D-的信號。串行接口引擎(SIE)主要用于解析協議層的USB規范,如時鐘提取、NRZI編碼/解碼、比特填充/抽取、CRC校驗、PID檢測/產生、串并/并串轉換等。功能控制器主要用于處理功能層的USB規范。緩沖區是功能控制器與SIE互相通信的橋梁,通常SIE把總線上接收到的數據存放在緩沖區中,供功能控制器讀取并解析;同時,功能控制器又會把需要發送的數據存放在緩沖區中,供SIE讀取并發送。

集成HUB的USB設備控制器又稱為復合設備控制器,它在本質上是兩個USB設備,在系統中擁有兩個不同的設備地址。因為USB是分時復用的串行總線,在正常情況下,任何時候主機都只能與系統中的某一個設備進行通信,所以復合設備控制器也可以把設備控制器和HUB控制器的很多部件合二為一,分時復用。

本文提出的集成HUB的全速USB設備控制器的設計方案如圖2所示。該控制器支持一個上行端口和四個下行端口,并實現了USB鍵盤的功能。SIE主要負責物理層和協議層的協議解析,MCU主要負責設備層的協議解析,緩沖區是SIE和MCU之間通信的橋梁,SIE把接收到的數據包存放在緩沖區中供MCU讀取,MCU把需要發送的數據存放在緩沖區中供SIE讀取。數據轉發功能主要由HUB 轉發器實現。

2 SIE設計

在USB HUB內部需要有一個全速SIE用來處理USB規范第八章規定的大部分協議,它的主要功能包括:

·包的識別與組織;

·時鐘與數據分離;

·NRZI編碼和解碼;

·比特填充和提取;

·CRC校驗碼的識別和產生;

·地址檢測;

·PID檢測和產生;

·串/并轉換和并/串轉換。

在設計SIE的時候,根據它的功能又將其分成幾個不同的模塊,如圖3所示。PHY模塊主要完成數據的串/并轉換和并/串轉換、比特填充和提取、NRZI編碼和解碼、時鐘與數據的分離等功能,此模塊內部數據主要以串行狀態存在。PL模塊負責數據包的解析與組織、PID檢測和產生、CRC檢驗碼的識別和產生、地址檢測等功能。FUNCTION模塊完成SIE與MCU的接口邏輯功能。

3 轉發器設計

轉發器是HUB實現數據轉發功能的核心模塊。轉發器實現的功能主要有:數據轉發、幀同步、掛起喚醒處理、總線沖突檢測與解決、往低速下行端口發送Keep-alive等。

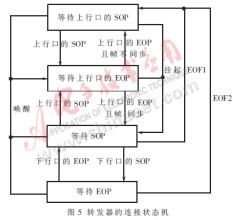

在設計轉發器的時候,根據數據的流向對轉發器進行了進一步的模塊細分,如圖4所示。hub_up模塊負責接收來自上行端口的信號,并檢測出SOP和EOP;同時轉發來自內部端口和下行端口的信號。hub_dp模塊包含四個子模塊,支持四個下行端口,負責接收來自下行端口的信號,并檢測出SOP和EOP;同時往下行設備轉發合法的下行數據。rpt_engine模塊中有一個重要的連接狀態機,其狀態轉換如圖5所示,它以數據包為單位控制上行端口和下行端口之間的連接的建立和拆除,同時控制集線器正確地掛起和喚醒。

?

在圖5所示的連接狀態機中,狀態跳轉主要通過SOP(包開始)和EOP(包結束)信號實現,所以SOP和EOP信號直接影響狀態機的正確跳轉,從而影響了轉發器的穩定性。檢測SOP信號時要考慮兩個重要的因素:首先,SOP信號要產生得盡可能快,從而可以較快地打開數據通道,減小數據流中SYNC的損失;其次,檢測與本地時鐘異步的數據流而產生的SOP信號要與本地時鐘同步,否則會使寄存器建立時間和保持時間得不到滿足。檢測EOP信號時也要考慮兩個因素:首先,要排除長度不夠的SE0的干擾和SE0狀態向J狀態跳變的抖動干擾;其次,EOP信號也要與本地時鐘同步。

全速HUB的上行端口始終是一個全速連接,但是它的下行端口可能是全速連接也可能是低速連接。低速數據經過上行端口時,雖然它的速率是低速的,但是它的極性卻是全速的。全速數據的極性與低速數據的極性是相反的,所以轉發低速數據時需要先對數據的極性進行轉換。HUB在轉發數據的時候需要遵循以下原則:來自上行端口的低速數據廣播給所有處于允許狀態的下行設備(包括全速設備和低速設備);來自上行端口的全速數據轉發給所有處于允許狀態的全速下行設備。

4 固件" title="固件">固件設計

本文提出的USB設備控制器是一個軟硬件結合的系統,即整個系統由MCU、SIE、轉發器等硬件和運行于MCU中的固件組成。

系統的設計原則是:凡是固件能夠完成的任務盡量由固件來實現,硬件的主要工作是對協議層的解析,解析完之后會設置某些控制寄存器,有時會產生中斷,固件通過查詢這些寄存器執行相應的操作。

為了驗證整個系統,通過編寫固件實現集成HUB的USB鍵盤的功能。

5 對于異步信號的處理

USB屬于異步總線,本地時鐘和主機時鐘是由兩個不同的晶振產生的,所以SIE必須采用適當的方法實現位同步" title="位同步">位同步。一個典型的位同步方法就是采用一種特定結構的數字鎖相環[1]。其原理是:分別用本地48MHz時鐘的正負沿采樣接收到的12MHz數據流,再用采樣后的信號控制狀態機的跳轉并產生12MHz的位接收時鐘(它的有效沿位于12MHz數據流每個比特位的中間),然后用新產生的時鐘去采樣12MHz的數據流從而實現位同步。

整個系統中采用的是異步復位" title="異步復位">異步復位。異步復位的好處是可以保證系統在初始狀態時處于已知的狀態,對于有三態總線的系統來說,這是非常重要的[2]。異步復位的處理非常重要,關系到系統的穩定性。對于異步復位信號來說,重要的不是什么時候復位而是什么時候復位結束,異步復位有兩個關鍵的參數恢復時間和遷移時間,如圖6所示[3]。如果以上兩個參數不滿足,就會產生亞穩態[4]。為了解決這個問題,設計了如圖7所示的復位電路。

在該電路中,復位的產生是不受時鐘控制的,但復位結束是受時鐘控制的。之所以要用兩個級聯的觸發器,是為了避免第一級觸發器有可能產生的亞穩態傳給整個芯片的復位信號reset。在這個電路中不存在恢復時間的問題,因為復位結束肯定在時鐘沿的后面。遷移時間的問題也可以解決,只要Tclk_q (clock to Q)+ Tpd(復位信號的傳輸延時) > Trem(觸發器的遷移時間)即可。對于上電復位來說還要進行進一步的處理,要保證復位時間足夠長,因為電源穩定需要一定的時間。

6 設備的低功耗設計

對于USB設備來說,當總線上超過3ms沒有總線活動時,設備就要自動進入休眠狀態,此時從總線上獲得的電流不能超過500μA[5]。為了滿足此要求,設計了如圖8所示的設備喚醒和休眠電路。

當設備需要休眠時,給出一個sleep信號控制晶體振蕩器(OSC)停止振蕩,整個設備進入節電模式。對于CMOS電路來說,時鐘停止振蕩以后所消耗的功率極小,當有總線活動時,收發器會產生總線活動標志信號wakeup,wakeup信號首先控制振蕩器重新開始振蕩,然后和clkDelay信號一塊控制設備的時鐘(Clock),晶振穩定后則輸出時鐘信號。復位時不對時鐘信號進行控制。

7 FPGA實現和系統驗證

系統進行實現和驗證時,串行接口引擎和轉發器采用Verilog進行RTL描述,然后采用Xilinx公司的XC2S200PQ208 FPGA實現。緩沖區和RAM由FPGA內部集成的RAM實現,收發器采用Philips公司的PDIUSBP11A,MCU采用MICETEK公司的65C02仿真器。

整個系統經驗證后,工作正常,內置鍵盤可以正常工作,在下行端口插入低速USB設備和全速USB設備都可以工作。圖9是用立肯科技公司的USBMobile測試儀對FPGA系統進行測試的結果的一部分。

參考文獻

1 Designing a Robust USB Serial Interface Engine(SIE). USB-IF.http://www.usb.org/developers/whitepapers/

2 Michael Keating, Pierre Bricaud. Reuse Methodology Manual for System-on-a-Chip Designs. Kluwer Academic Publishers,2000

3 Design Compiler Manual. Synopsys Corp., 2003

4 Mike Stein.跨越鴻溝:同步世界中的異步信號.EDN電子設計技術,2004 (7)

5 Universal Serial Bus Specification 1.1. Compaq, Intel, Mi-crosoft, NEC,1998-09-23