??? 摘 要: 介紹了XGA標準,設計了一種基于FPGA的XGA標準圖像實時控制器,它將PAL制式的電視信號轉換成XGA格式的信號。重點討論了圖像數據的結構轉換過程及控制器的內部結構。

??? 關鍵詞: XGA? FPGA? 雙端口" title="雙端口">雙端口RAM? 圖像轉換控制器

?

??? 可編程邏輯器件FPGA由于具有開發簡單、靜態可重復編程和動態在系統編程的特點,已經成為當今應用最廣泛的可編程專用集成電路(ASIC)。而XGA(eXtended Grophics Adapter)顯示器因其輸出信息量大、輸出形式多樣等特點已經成為目前大多數設計的常用輸出設備,在FPGA的設計中可以使用很少的資源,就能產生XGA各種控制信號。

1 VGA原理和XGA標準

??? 計算機顯示器的顯示有許多標準,常見的有VGA、SVGA、XGA等。常見的彩色顯示器一般由陰極射線管(CRT)構成,彩色是由R、G、B三基色組成,用逐行掃描的方式進行圖像顯示" title="圖像顯示">圖像顯示。陰極射線槍發出電子束打在涂有熒光粉的熒光屏上,產生R、G、B三基色,合成一個彩色像素。掃描時從屏幕的左上方開始,從左到右、從上到下進行掃描。每掃完一行,電子束回到屏幕的左邊第一行的起始位置。在這期間,CRT對電子束進行消隱,每行結束時,用行同步信號" title="同步信號">同步信號進行行同步;掃描完所有行,用場同步信號進行場同步,并使行掃描回到屏幕的左上方,同時進行場消隱,預備下一場的掃描。對于普通的VGA(Video Graphics Adapter(Array))顯示器,其引出線共有五種信號:三基色信號(R、G、B);行同步信號(HS);場同步信號(VS)。

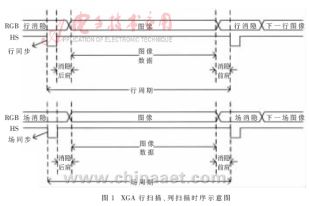

??? 對于VGA顯示器的這五種信號的時序驅動要嚴格遵循“VGA工業標準”,本設計中采用1024×768@60Hz的XGA標準。圖1是XGA行掃描、場掃描的時序圖,表1、表2分別為行掃描、場掃描的時序要求。

??????????????????

??? 設計XGA顯示控制主要注意兩個問題:一個是時序驅動,這是完成設計的關鍵,時序稍有偏差,顯示必然不正常,甚至會損壞彩色顯示器;另一個是XGA信號的電平驅動(XGA信號的驅動電平是模擬信號)。

2 控制器的設計

2.1 控制器原理

??? 本設計的數據源是PAL制式的電視信號,數據格式為YUV(4:2:2)格式。本設計以FPGA為平臺,將原始的電視信號數據轉換為RGB格式的視頻信號,并使圖像的分辨率由720×576提高到1024×768,達到XGA標準。設計可分為FIFO模塊、雙端口RAM控制模塊、圖像結構轉換模塊和色空間轉換模塊。設計選取的雙端口RAM必須能存儲兩幀以上圖像,以保證完成緩沖。當雙端口RAM從一端寫滿一幀圖像數據后,在寫滿下一幀數據前,開始從另一端讀取第一幀數據;第二幀寫滿后再讀取第二幀,直到第一幀的數據被第三幀數據完全覆蓋,不斷重復此過程。圖像結構轉換模塊和色空間轉換模塊將PAL制式(分辨率720×576,場頻50Hz,隔行掃描)的電視信號轉換為XGA(分辨率1024×768,幀頻60Hz,逐行掃描)標準的視頻信號。

2.2 硬件實現

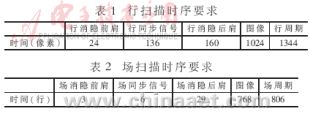

??? 本設計中FPGA采用了Actel公司的APA150芯片。該FPGA芯片具有150 000個系統門,邏輯單元為6144個,內嵌36KB的雙端口SRAM的2個鎖相環PPL內核,最大支持242個用戶I/O(I/O電壓有3.3V和2.5V兩種可供選擇),支持3.3V、32bit、50MHz的PCI總線,系統時鐘最高為32MHz。雙端口RAM采用賽普拉斯半導體公司(Cypress Semiconductor Corp.)的CYD18S72V雙端口RAM,該芯片容量為256K×72bit,其硬件框圖如圖2所示。

????????????????????????????

2.3 雙端口RAM控制模塊

2.3.1 雙端口RAM簡介

??? 雙端口RAM作為一種特殊類型的RAM,在一些高速數據采集與處理系統中得到了廣泛應用。它具有兩個獨立的端口,各自均有一套相應的數據總線、地址總線和控制總線,允許兩個端口獨立、異步地對存儲器中的任何存儲單元進行存取操作。當兩個端口同時對存儲器中的同一單元進行存取操作時,可以由其內部仲裁邏輯決定優先權。

2.3.2 雙端口RAM的控制

??? 當兩個端口對雙端口RAM存取時,一般存在四種情況:(1)兩個端口同時對不同地址單元讀寫數據;(2)兩個端口同時對同一地址單元讀出數據;(3)兩個端口同時對同一地址單元寫入數據;(4)兩個端口同時讀寫同一地址單元,一個寫入數據,另一個讀出數據。

??? 在(1)、(2)兩種情況下,兩個端口的存取不會出現錯誤,(3)、(4)種情況時會出現競爭現象。為避免因競爭而導致的通信錯誤,可采取“BUSY”功能輸出或通過特殊的軟件處理方法來解決。在本設計中,雙端口RAM僅用來作為數據緩沖,一個端口輸入,另一個端口輸出,只要避免出現第四種情況即可。在實現時,將雙端口RAM分成兩個工作區,每個工作區可以存儲一幀的圖像數據。當輸入端口輸入的數據寫滿工作區1后,在寫滿工作區2前,通過程序控制輸出端口反復從工作區1中讀取數據;當工作區2寫滿后,在輸入端口的數據重新寫入工作區1、工作區1寫滿前,通過程序控制輸出端口反復從工作區2中讀取數據。多次重復上述過程,可以實現對圖像數據的無差錯存取。

??? 在存儲時,要將電視信號的一個奇場和一個偶場的行像素數據交錯存儲,這樣就實現了由隔行到逐行掃描的結構轉換。本設計中采用的雙端口RAM為256K×72bit的存儲器,而YUV數據格式為每個像素16bit數據,每行720個有效像素,每行像素占用160個地址,因此每幀圖像占92 160個地址。

2.4 時序產生器模塊

??? 視頻定時產生器產生正確顯示圖像所必需的同步信號——行同步信號、場同步信號。利用FPGA內部時鐘鎖相環倍頻后的65MHz的主時鐘,來產生符合XGA標準的視頻信號,其分辨率為1024×768、幀頻為60Hz。

????行同步過程的時間以像素節拍為單位進行測量,用一個計數器控制。計數器對輸出的像素進行計數,復位后從0開始,此時圖像顯示處于有效狀態;計到1024時,開始進入行消隱前肩狀態;計數到1048時,進入行同步狀態;計數到1148時,進入行消隱后肩狀態;計數到1343后,在下個像素節拍到來時計時器清零,重新進入圖像顯示有效狀態。

??? 場同步過程的時間以行節拍為單位進行測量,也用一個計數器控制。計數器對輸出的行進行計數,復位后從0開始,此時圖像顯示處于有效狀態;計數到768時,開始進入場消隱前肩狀態;計數到771時,進入場同步狀態;計數到777時,進入場消隱后肩狀態;計數到805后,在下個像素節拍到來時計時器清零,重新進入圖像顯示有效狀態。

2.5 FIFO模塊

??? FIFO1(先入先出)是深度為1024、寬度為16位的異步FIFO,寫時鐘為YUV信號的輸入時鐘PCLK,讀時鐘為時鐘發生器產生的主時鐘MCLK。當輸入的原始數據的行、場同步信號都有效時,該FIFO的寫使能有效;當寫地址計數器數到一半或計滿時,觸發讀使能信號,使讀使能信號在后面的360個讀時鐘周期內一直有效。由于讀時鐘頻率大于寫時鐘頻率,所以不會產生數據寫滿溢出的現象。

??? FIFO2、FIFO的設計與FIFO1類似,為深度為1024寬度為16位的異步FIFO,寫時鐘為主時鐘。FIFO2、FIFO3在主時鐘的同步下交替按行接收從雙端口RAM中讀出的數據,當快寫滿時停止從雙端口RAM中讀數據,同時FIFO的寫使能信號無效,讀使能信號有效。當快讀空時,觸發寫使能信號,繼續讀取數據。

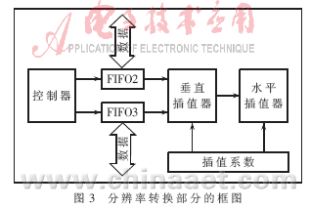

2.6 圖像結構轉換模塊

??? 該模塊要完成分辨率的轉換,以及幀頻的轉換。

2.6.1 分辨率的轉換

??? 原始信號的分辨率為720×576,目標分辨率為1024×768。轉換的方案是:首先將原始信號做3:4的放大,使像素點數變為960×768,再將每行的兩側各補充32個0,這樣既達到了1024×768的分辨率要求,算法也比較簡單。考慮到一般只注意圖像中間部分,對四周不是很關心,因此,在放大圖像四周補0的做法不會影響圖像的效果。

??? 水平方向插值" title="插值">插值采用三次樣條插值,垂直方向插值采用相鄰兩行內插" title="內插">內插算法,內插函數采用bisigmoidal[5]函數:

???  ?

?

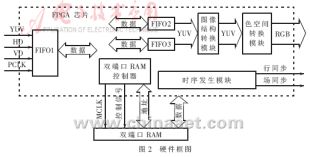

式中,a是調節曲線特性的常數,?駐y是函數輸入變量。采用臨近兩點y(n+1)和y(n)進行插值的公式如下:

???

式中,K=h(Δy)。

??? 為了避免非線性插值系數給電路設計帶來的復雜性,將內插系數存儲于查找表中,根據內插點與臨近點的相對位置找到對應系數。

??? 分辨率轉換部分的框圖如圖3所示。

????????????????????????

??? 在插值時,首先將第一行數據輸入FIFO2,第二行輸入FIFO3,兩個FIFO交替將數據輸入垂直插值器,垂直插值器按行輸出垂直插值后形成的行數據,輸入到水平插值器。FIFO共輸入3行后,FIFO停止向垂直插值器一個節拍,垂直插值器將輸出4行像素數據;水平插值器每讀取3個像素數據時停止一個節拍,從而根據不同插值系數和臨近點數據插出4個值,從而完成3:4的放大。在輸出放大后的行數據時,在行的左端和右端各添加32個零點,這樣就完成了分辨率的轉換。

2.6.2 幀頻的轉換

??? PAL制式每秒奇偶共50場,經過雙端口RAM的存儲后整理為每秒25幀,要轉換為能夠滿足每秒60幀要求的視頻信號,最簡單的辦法就是復制幀。在本設計中,上一小節中轉換分辨率后的數據傳遞給色空間轉換模塊的同時,存入一個存儲器中,在下一幀數據處理完成前,將存儲器中的數據再次傳輸指定的次數,從而完成幀頻的轉換。幀頻比為5:12,所以每5幀做一次頻率放大,第一幀、第三幀傳輸3次,其余各幀傳輸2次。

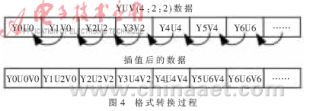

2.7 色空間轉換模塊

??? 該模塊接收到的信號是YUV(4:2:2)格式的信號,是16位數據線,而要將它轉換成的RGB信號是24根數據線,就需要先將每個像素點上丟失的色差信號補回來,即16根數據線加寬到24根。格式轉換過程如圖4所示。

????????????????????????

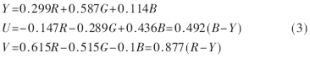

??? 接下來要完成的是由YUV到RGB的色空間轉換,轉換公式如下[6]:

???  ?

?

??? 在計算時必須把它們都轉換成整數,所以在程序中利用位移寄存器,讓它們左移11位,計算后即可得到RGB數據。

??? 采用FPGA技術設計的VGA圖像控制器,大大減少了電路板的尺寸,充分應用了FPGA快速并行處理數據的特性(這是其他控制器所不可比擬的),在產生同步信號的同時送出像素數據,同時增加了系統的可靠性和設計靈活性。解決了嵌入式系統實時圖像顯示的問題,節約了成本,擴展了應用范圍。

參考文獻

[1] 李國剛,余俊,凌朝東.基于FPGA的VGA圖形控制器的實現方法.信息技術,2006,(7).

[2] 方湘艷,韓威.基于FPGA技術的異步雙端口RAM設計與實現.中國集成電路,2005,(1).

[3] 吳蓬勃,張啟民,王朝陽,等.基于FPGA的VGA圖像控制器設計.東北電力大學學報,2006,(8).

[4] 潘松,黃繼業.EDA技術與VHDL.北京:清華大學出版社,2005.

[5] LEE J.Design of a scan format converter using the bisigmoidal interpolation[J].IEEE Trans Consumer Ilectronics,1998,44(3):1115-1120.

[6] Xilinx Inc.Colour space conversion.XAPP637[Z],2002.