目前采用的LED大屏幕顯示系統的控制電路大多由單個或多個單片機及復雜的外圍電路組成,單片機編程比較復雜,整個電路的調試比較麻煩,可靠性和實時性難以得到保證。針對這種情況,本文提出了一種基于SPCE061A和Cyclone EP1C6的LED大屏幕解決方案。該設計方案無須外掛FLASH ROM和RAM,無須任何外部功能電路,所有功能均由一片EP1C6和一片SPCE061A實現,數據處理速度快、可靠性高。

SPCE061A和CycloneEP1C6簡介

SPCE061A是凌陽科技的一款16位微控制器,內嵌32KB閃存和2KB字SRAM。CPU最高可工作在49MHz的主頻下,較高的處理速度使SPCE061A能夠非常容易、快速地處理復雜的數字信號。本文設計的是一個點陣大小為192×128的單色(紅色)顯示屏,且按要求連續顯示5屏數據,SPCE061A豐富的片內資源正好滿足了如此大的數據處理和存儲要求。本文采用由UART中斷接收上位機數據并將數據寫入32KB閃存中的方法,取代了傳統MCU+ROM+RAM的設計,增加了系統的穩定性。

Cyclone EP1C6是Altera推出的一款高性價比FPGA。該器件提供的具有異步、雙端口、帶寄存器輸入口、可選擇的帶寄存器輸出口的存儲模塊—M4K在本設計中被設置成一個雙口RAM,實現數據的讀寫同步,提高了系統的刷新頻率。

整體設計方案

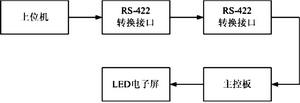

本系統設計的是一塊具有192×128個紅色LED點陣的電子大屏幕。整塊大屏幕是模塊化的結構,每4個16×16的點陣塊為一個最小模塊,每行點陣由3個同樣的最小模塊級聯而成,共8行。大屏幕上要求連續顯示5屏內容,且每屏都具有上下左右移動等動畫效果。實際應用中主控制室距離電子屏約為200米。結合設計對象的要求和大屏幕設計的特點,本文提出了一種新穎的設計方案。該方案的整體框圖如圖1所示。

圖1 系統框圖

LED大屏幕系統由3個主要單元組成:上位機圖像/文字編輯與發送部分單元、主控板單元、顯示驅動電路單元。系統上位機由一臺PC機來控制,它主要編輯、發送圖像/文字信息到主控板的存儲器中;主控板對這些字模數據進行處理后發送到大屏幕,并在大屏幕上顯示出來。

系統硬件設計

上位機發出的信息經符合RS-422標準的接口通過雙絞線傳送到主控板上,通訊速率可在上位機軟件中設置。接口所用芯片為MC3487和MC3486,RS-422在傳輸速率為100kb/s時,可傳輸的最大距離為1200米。本系統的傳輸距離約為200米,傳輸速率最大為115kb/s,采用RS-422方式傳輸可滿足這一長距離通訊的要求。

主控板單元設計

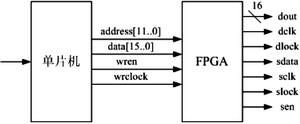

該單元的設計特點在于數據流接收、存儲以及驅動掃描的單片集成,無須任何外圍電路。主控板由一片SPCE061A和EP1C6組成,如圖2所示。

&

nbsp; 圖2 主控板框圖

該單元的設計思路是,由單片機的IOB7口以UART中斷的方式接收上位機發送的數據。這是由于大屏幕處于被動、循環往復的顯示狀態,采用異步傳輸能減少系統不斷查詢串口接收標志位的系統消耗。單片機將接收的串口數據以兩個字節為單位逐一寫入內置的閃存中。單片機內部的2KB SRAM作為緩存區,每當單片機要向FPGA中寫一屏新的數據時,先按特定的地址從閃存中讀出數據并存放到SRAM中,再將SRAM中的數據并行寫到FPGA的雙口RAM中。單片機與FPGA的接口信號除了16根數據線外,還包括單片機向FPGA寫數據的地址、寫使能和寫時鐘。由于每屏的點陣數為192×128,16位數據并行傳輸所需的地址線為11根。但由于設計需要,系統中還專門設置了1根額外的地址線,用于對FPGA的雙口RAM進行讀寫分區,因此共使用了12根地址線。

FPGA在其內部配置一個雙口RAM緩存單片機寫入的數據,同時將這些數據按照大屏幕的結構和掃描電路的特點選擇性地讀出,然后對數據由并轉串輸出到大屏幕的掃描驅動電路。由于大屏幕采用模塊化的隔行掃描方式,每行需要2根數據線進行隔行傳輸,整塊大屏幕共需16根數據線。由于點陣的行列驅動均采用74LS595驅動,故FPGA還應產生列掃描的點時鐘、鎖存信號和行掃描的數據、時鐘、鎖存信號。

雙口RAM的配置

由于數據顯示是一種動態掃描方式,如果采用一個RAM區,當單片機寫RAM 時,FPGA只能處于等待狀態,這樣就會導致屏幕動態掃描停止。由于屏幕數據是移位輸出的,當掃描停止時,因為會有某一行的高電平保持較長的時間,該行就會一直保持較強的亮度,影響屏幕的顯示效果。本系統中設計了2個同樣大小的RAM 區:A區和B區,讓單片機交替進行寫操作。當單片機在寫A區時, FPGA就去讀B區的字模數據;當單片機寫B區時,FPGA就去讀A區的字模數據。這樣就不會造成FPGA的停止掃描,保證了各行的點陣有相同的時間占空比,使屏幕點陣有同樣亮度。單片機中的 HIGHADR引腳可用于控制單片機的寫區和FPGA的讀區。

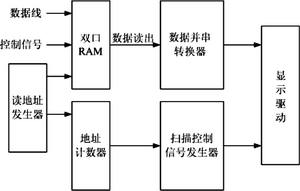

由于每屏點陣數據的大小為1536字,A區和B區的容量都至少要大于1536,那么整個的RAM區至少為1536×2字。考慮到EP1C6內部集成了20塊容量為256字的M4K模塊,正好可以滿足本系統對RAM的需求。雙口RAM的配置如圖3所示。

圖3 雙口RAM配置

其中wren是單片機往FPGA中寫入數據的寫使能信號,wraddress[11..0]是寫地址信號, wrclock是寫時鐘,data[15..0]是寫數據,rdaddress[11..0]是讀地址信號,rdclock是讀數據的時鐘信號,q[15..0]是讀出的數據。對于這個雙口RAM而言,只有q[1

5..0]是輸出端口,其它均為輸入端口。與寫數據相關的信號全部由單片機產生,讀數據的所有信號由FPGA產生。其中讀寫地址的最高位可實現RAM分區。

點陣驅動電路

本系統中LED的灰度等級是采用調制占空比的方法來實現的,由于大屏幕是單色點陣,主要用來顯示文字信息,所以要求亮度高且均衡。根據這一特點,采用了模塊化的隔8行掃描方式。每隔8行點陣同時進行掃描,則每行的占空比是1/8,使屏幕亮度得到保證。

點陣的驅動電路分為行驅動和列驅動,列驅動采用串行數據傳輸方式,易于模塊化。列驅動電路由74LS595組成,行驅動電路由74LS595和與之配套的反相器7406、PNP達林頓功率三極管TIP127組成。所有作為行驅動74LS595的數據時鐘信號、數據鎖存信號、掃描數據、時鐘、鎖存信號都在一起,所有作為列驅動74LS595的數據時鐘信號、數據鎖存信號、掃描數據、時鐘、鎖存信號也是在一起的,這樣可以實現大屏幕的同步顯示。

軟件設計

系統的軟件設計由3部分組成:上位機圖像/文字編輯與發送軟件設計、單片機控制單元軟件設計,以及FPGA控制單元軟件設計。

上位機軟件設計

上位機的圖像/文字編輯與發送軟件由Visual Basic編寫,只須在界面中將屏幕大小設置為192×128,串口選擇COM1或COM2,波特率設置為9600,并設置每屏的起始地址和要發送的屏數,調入包含相關信息的文件,點擊“發送”按鈕即可。數據流經符合RS-422標準的雙絞線傳輸到主控板。該軟件適用于任何大小的彩色/單色屏,提供了豐富的圖形/文字編輯、修改功能。也可以直接調用Windows中的16色畫圖文件(*.bmp),從而可以利用Windows或基于Windows的各種作圖工具設計出豐富多彩的圖像。

單片機控制單元軟件設計

單片機控制單元的軟件設計主要實現3大功能:串行數據接收、數據輸出和圖像顯示方式變換。設計流程如圖4所示。串行數據接收部分主要是通過UART中斷接收并保存位圖文件。圖像顯示方式變換部分實現圖像的變換,如上移、下移、左移、右移等,以實現豐富多彩的圖像顯示效果。

圖4 主程序流程圖和中斷程序流程圖

FPGA控制單元軟件設計

FPGA控制單元是在QUARTUSII環境下開發的,主要功能是配置雙口RAM、傳送數據和相應的驅動信號,以實現串行數據的顯示。串行數據顯示是軟件設計的核心,該單元的軟件設計模塊如圖5所示。雙端口RAM的配置完全由軟件實現,FPGA讀雙口RAM的A區還是B區是由單片機的HIGHADR引腳控制的。FPGA按照顯示驅動的要求讀出相應的數據后,還要將這些數據由串轉并送至列驅動的74LS595上。掃描控制信號則在數據送到顯示驅動的過程中產生,用于實現行、列驅動。

圖5 FPGA控制單元軟件設計框圖

結語

本文提出的基于Cyclone EP1C6和SPCE061A 的LED 大屏幕方案已應用于現場。其基于FPGA的雙口RAM 和掃描控制設計使得系統穩定可靠。實踐證明,本系統能以多種播出方式顯示各種字體和型號的文字和圖形信息,與同類設計相比,畫面清晰、性能穩定、操作使用簡單,具有很好的應用前景。