將可編程邏輯與CPU子系統集成于同一芯片令系統設計者可以在一定范圍內決定某些功能的實現方式,AES先進加密標準算法的硬件實現即為這樣的特殊應用實例。AES加密是互聯網協議安全規范(IPsec)的基礎模塊,提供增強無線連接安全性的IEEE802.11i規范也采納AES為其加密算法,因而傳統通訊設備供應商需要增加AES模塊以提供更全面的VPN服務。由于AES算法直接面向位操作,所以,它在可編程邏輯上可以得到非常高效的實現。

分析儀及其工作環境

FS2(First Silicon Solutions)公司的在系統分析儀支持基于QuickLogic公司的嵌入式標準產品QuickMIPS的單片系統硬件和軟件開發。除了完全支持QuickMIPS片上MIPS處理器的所有調試功能之外,該分析儀還內建可配置邏輯分析監控單元(CLAM),該單元可以從片外追蹤并觸發QuickMIPS可編程邏輯的1024個指定信號。FS2探測器可通過14針EJTAG調試連接頭以及1根10針(或38針)的追蹤電纜來連接目標系統。QuickMIPS可編程邏輯中的片上儀器應用模塊(OCI)通過FS2追蹤電纜與用戶指定的內部信號相連,用于追蹤和觸發。

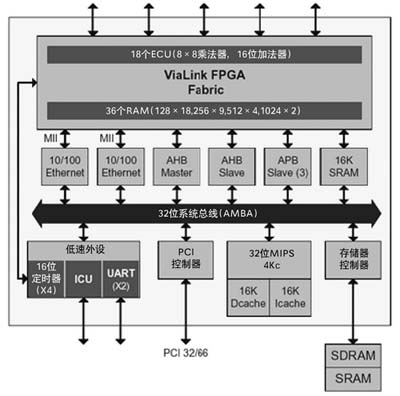

除可編程邏輯之外,QuickMIPS內還集成了32位MIPS 4Kc處理器和一系列片上外設。這些片上外設包括2個以太網接口、2個串口、1個32位66MHz的PCI

主從接口、1個SDRAM和SRAM控制器、4個定時器以及1塊片上SRAM。所有外設、處理器和可編程邏輯均通過AMBA總線連接(見圖1)。AMBA總線為這些連接提供5個片上可用端口,包括先進高性能總線(AHB)主/從接口各1個以及3個先進外圍總線(APB)從接口。任何實現于可編程邏輯的電路均可通過上述片上AMBA總線端口實現與處理器以及片上外設的連接,設計者可以根據實際需要使用上述5個端口中的不同組合來連接電路。QuickMIPS的片上MIPS處理器也支持增強JTAG(EJTAG)接口。EJTAG接口除支持處理器實現中止、單步、重啟以及軟件斷點等調試功能之外,還包括指令/數據虛擬地址、硬件斷點以及支持外部EJTAG探測儀的TAP端口。

圖1 QuickMIPS片上可用資源框圖

圖2 硬/軟件交互觸發示意圖

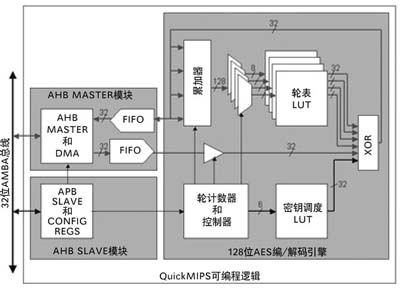

軟硬件協同AES算法主要由查找表和異或邏輯構成,因此它非常適合用可編程邏輯實現。在本文中,AES的編解碼算法由可編程邏輯實現,而密鑰調度(key schedule)和輪查找表(round LUT)則由CPU生成。一旦CPU完成了查找表的生成,就可以利用編解碼函數將輸入的任意大小的明文編碼為連續的密文流輸出。

基于連續報文流的數據吞吐需要,在可編程邏輯中還建立了一個DMA引擎,用于從/向AES核下載/上傳報文,并直接處理與系統存儲器之間的通訊。該DMA引擎能夠操作連接在QuickMIPS器件上的任何存儲器,包括片上SRAM和片外SRAM/SDRAM。使用DMA引擎可以避免無用的等待周期,從而高效運用AES核進行連續的編解碼操作。

該DMA引擎使用1個AMBA總線的AHB主控制器,用于連接簡單的AES核數據輸入/輸出接口和相對復雜的AHB主接口。它還包含2個用于AMBA總線與AES模塊之間異步數據緩沖的128×32位的FIFO,以保證在AMBA總線受制于CPU的工作頻率時,AES仍可獨立工作于最佳頻率。

存儲源地址、目標地址、DMA傳輸塊大小、DMA傳輸使能和AES編解碼模式轉換等控制信息的寄存器也可用可編程邏輯實現,CPU可以用它們來設置DMA引擎和配置AES核。這些控制寄存器通過APB從接口連接在AMBA總線上。

除連接DMA和AES的控制寄存器之外,APB接口還可用于在AES核內加載存儲了不同查找表數據的RAM模塊。這些查找表中的靜態模式(static pattera)和密鑰調度用于AES算法中不同的輪,它們 由AMBA單向寫入,并由AES模塊單向讀出。

系統調試

由于硬件和軟件的調試方法往往格格不入,如時間難于同步、調試方式迥異,及調試階段難于交互通訊等,因此,調試由硬/軟件模塊交互構成的系統非常困難。基于QuickMIPS的FS2硬/軟件協同調試方案可以有效解除上述困擾(見圖2)。

EJTAG探測儀通常用于監控CPU的執行進程,然而一旦整合系統被分拆為交互操作的硬/軟件模塊,那么,在缺乏有效硬件監控手段的情況下,硬/軟件模塊間交換數據進程的調試工作的復雜程度就顯著提高了。

在硬/軟件協同的AES解決方案中,EJTAG探測儀可用來監控CPU生成密鑰調度和復制可編程邏輯中的RAM模塊數據的進程,此外,EJTAG還可以監控CPU設置DMA引擎的過程。EJTAG探測儀的強大功能保證了用戶對源地址、目標地址和CPU讀寫可編程邏輯時的數據傳輸的監控。一旦AES系統的硬件部分實現了,CLAM即可監控CPU通過AMBA總線對可編程邏輯進行的操作。這里,CLAM將監控包括AHB主接口和APB從接口的所有相關AMBA總線信號。被監控的總線調用事件包括:通過APB從接口加載RAM

模塊中的密鑰調度和輪表,并設置DMA地址和控制寄存器;通過AHB主接口以DMA方式將明文從遠程AMBA從設備傳送到AES核,并將密文從AES核傳送到遠程AMBA從設備。

一旦可編程邏輯中實現了OCI模塊,通過監控AMBA總線信號,任何AMBA總線上的事件均可被CLAM準確甄別、觸發和捕獲。能夠準確捕獲AMBA總線信號狀態的觸發器可以被定義為AMBA總線信號的任意組合。例如將向特定的AMBA地址進行的寫操作設為觸發事件,就可以捕獲加載RAM模塊狀態;而將觸發點置于APB對寄存器空間的選擇信號上,則可以捕獲DMA地址和控制寄存器的設置狀態;最后,對內部AMBA仲裁單元給出的AHB主接口設定觸發,就可以捕獲DMA傳輸事件。用戶可以根據這些捕獲結果來判斷AMBA總線的操作是否符合要求。

AES應用模塊的調試需要監控以下信號:輸入AES核的明文,輪表RAM模塊的索引(地址)輸入和數據輸出,計數器輸出的當前輪數和每一輪中的數據狀態,密鑰調度RAM模塊中的數據輸出,及128位累加器輸出。

通過OCI鎖定監控上述信號可以詳盡地觀察到AES核的操作。由于可以同時對數百個信號以不同追蹤深度進行監控,用戶可以毫無困難地捕獲和觀察AES編/解碼的所有44個周期。例如,如果大多數AES轉換都正確執行,但是在某一個輸入報文模式下發現了意外的結果,在這種情況下,CLAM能夠配置特定報文進入AES引擎時的觸發。雖然在觸發產生前后會出現數百個AES轉換,但是CLAM可以實時地從中選出所需的那個事件,就無需為此去專門向系統提供一份輸入數據了。

交互觸發

交互觸發是EJTAG調試器與CLAM協同調試解決方案中最重要的特點。交互觸發分為2種方式,CLAM的觸發事件能夠使CPU在執行代碼的相應行中斷,同時CPU執行中的斷點也能夠觸發CLAM事件。

上述第1種交互觸發事件可以應用在軟硬件協同AES系統的調試過程中,例如尋找被寫入密鑰調度RAM的異常數據時。如果已知異常數據正在向RAM中寫入,且此數據可以被觀測到,并可被CLAM觸發,則可以通過觸發導致CPU

在數據寫入的時候暫停執行。由于密鑰調度的生成和其加載入RAM的過程都由CPU控制,因此可以在代碼中找到異常數據進入AES核硬件部分的那個時刻。這樣使得用戶可以查詢到那個時刻的存儲器和寄存器中的數據,在調試軟件算法的同時觀測到硬件上出現的結果。

第2種情況適用于用戶打算觀測指定軟件斷點處的可編程邏輯中正在傳輸的數據時。例如當CPU正在處理要寫入RAM的數據表時,用戶可能需要在數據傳送到硬件之前進行一些字節交換(byte swap)的操作。在調試時,用戶可以在源代碼中的字節交換部分,或是在結果輸出至AMBA總線時設置斷點。當字節交換的結果寫入硬件部分時,這些數據就可以通過AMBA從接口進行觀察。雖然沒有設置硬件觸發,但是軟件中的斷點可以使當時的硬件狀態被捕捉到。

結語

嵌入式標準產品平臺的高速發展需要 與之相應的精確周密的調試工具也隨之發展。對CPU與可編程邏輯共存的SoPC而言,用于調試CPU時的傳統的JTAG方法和FPGA的邏輯分析同樣需要,更重要的是有交互觸發的硬/軟件環境,以便快速地隔離、甄別并調試復雜問題。理想的SoPC系統分析工具應該能夠處理上述問題,并且提供監控系統內部總線事件的能力。

為了避免調試工具擾亂系統的正常操作,對系統內部總線事件和FPGA內部信號的監控、追蹤和觸發絕不能暫停和干預CPU的工作。因此,可以獨立或者協同調試CPU與FPGA的工具是目前最有效的SoPC系統分析方法。

在本文中,FS2公司的在系統分析儀和QuickLogic公司的QuickMIPS器件的配合使用,以及軟硬件系統AES引擎的實例提供了精彩的案例平臺,充分體現了上述這些先進的調試技術對復雜SoPC系統設計分析的重要性。