摘 要:本文提出了一種基于FPAG芯片的控制系統設計方案。系統中利用FPGA狀態機高效地控制ADC進行信號采集。在FPGA中搭建的模糊控制器通過對勵磁電流的連續調節,實現了恒速、恒轉矩和恒流等控制策略。

引言

電渦流緩速器的工作原理基于電磁感應理論。作為一種輔助制動裝置,其減少了主制動裝置的機械摩擦,既提高了壽命,又提高了車輛行駛的安全性、經濟性和舒適性,越來越受到汽車制造廠家的青睞。但是,由于汽車領域對實時性要求較高,且模糊控制算法涉及到頻繁的多字節數據的乘除運算,而FPGA在實現算法方面具有巨大的優勢,因此本文將基于FPGA進行設計。另外,本文結合基于FPGA的32位精簡指令軟核Nios編程,能很好地解決實時性與控制靈活性之間的矛盾。

節能型電渦流緩速器

目前大部分電渦流緩速器利用蓄電池或自帶發電機來產生勵磁電流,這兩種方法在緩速時都不能最優化地將車輛所具有的動能轉化為剎車能量。

本系統根據電渦流緩速器制動力矩的大小對自發電機和蓄電池進行調度,電渦流緩速器制動力矩公式如下:

這里,lg為氣隙間距; d為鐵心直徑;R1為勵磁線圈中心點的半徑;Np為磁極對數; N為勵磁線圈繞組匝數;I為勵磁線圈繞組電流;r為轉子盤電阻率;mr為轉子盤相對磁導率;w為轉子角速度。

當車速較大時,自發電機在一定電壓下的輸出電流大于I,將一部分電能用于制動,剩下的電能儲存到蓄電池;當車速較慢時,自發電機在一定電壓下的輸出電流小于I,則從蓄電池輸出電流到繞組線圈產生勵磁電流,從而最大限度地利用能源。

基于FPGA的電渦流緩速器控制系統

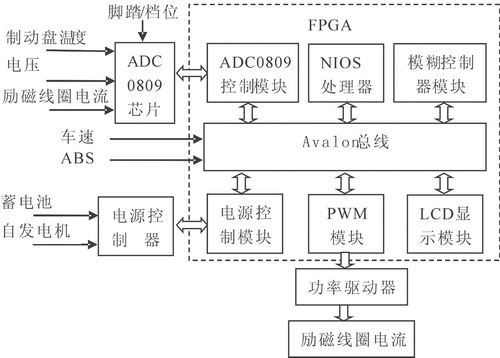

為了提升系統可靠性和靈活性,本控制器根據功能需求進行模塊化設計,主要包括ADC0809控制、NIOS處理器、模糊控制器、電源控制、PWM、LCD顯示等模塊,系統結構如圖1所示。

圖1 電渦流緩速器控制系統結構

系統首先由ADC0809控制模塊控制ADC進行各種信號,如溫度、電壓等信號的采集,然后通過Avalon總線把數據傳輸到模糊控制器、電源控制等模塊。電源控制模塊根據車速會對蓄電池和自發電機進行能量調度,實現最大限度的節能;模糊控制器模塊根據恒速、恒流等控制策略,計算出用于控制PWM占空比的參數,實現勵磁電流的調節。

ADC0809控制模塊

信號采集是系統實現閉環控制的重要環節,它的好壞關系到整個系統的性能。采用FPGA控制ADC的方式能有效降低外界干擾對采樣造成的影響,提高可靠性。另外,利用FPGA狀態機產生的時序控制ADC時,控制周期短、速度快,能提高整個系統的實時性。

使用狀態機控制ADC0809芯片采樣,包括時序控制和數據的讀取。首先,狀態機輸出兩路信號先后控制引腳ale和start,一旦start有效,狀態信號EOC即變為低電平,表示進入轉換狀態,狀態機通過不斷檢測ADC0809引腳EOC的電平來判斷轉換是否結束。若EOC為高電平表示轉換結束,狀態機輸出信號使引腳OE由低電平變為高電平,最后讀取轉換好的數據,主要Verilog代碼如下。

always @ ( EOC ,state )

begin case ( state )

st0 :begin ale <= #1 1'b0; start <= #1 1'b0; OE <= #1 1'b0; state <=#1 st1; end

st1 :begin ale <= #1 1'b1; start <= #1 1'b0; OE <= #1 1'b0; state <=#1 st2; end

st2 :begin ale <= #1 1'b0; start <= #1 1'b1; OE <= #1 1'b0; state <=#1 st3; end

st3 :begin ale <= #1 1'b0; start <= #1 1'b0; OE <= #1 1'b0;

state<=(EOC==1'b1)? #1 st3:st4; end

st4 :begin ale <= #1 1'b0; start <= #1 1'b0; OE <= #1 1'b0;

state<=(EOC==1'b0)? #1 st4:st5; end

st5 :begin ale <= #1 1'b0; start <= #1 1'b0; OE <= #1 1'b1; state <=#1 st6; end

st6 :begin ale <= #1 1'b0; start <= #1 1'b0; OE <= #1 1'b1; state <=#1 st0; end

default : begin ale <= #1 1'b0; start <= #1 1'b0; OE <= #1 1'b0; state <=#1 st0; end

endcase end

模糊控制器模塊

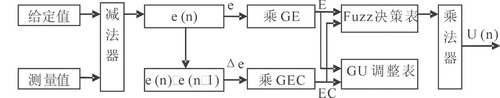

電渦流緩速器是一個非線性系統、強耦合、模型較復雜的對象。由于常規PID控制不具備在線調整參數的功能,所以不適于勵磁電流與車速呈非線性關系的系統控制。而模糊理論具有很強的非線性建模能力,能完成復雜系統的非線性映射功能,將模糊推理機制引入到測控系統中,實現對電渦流緩速器的最佳控制,以滿足實際的行車情況,控制器原理圖如圖2所示。

圖2 模糊控制器原理圖

從原理圖可以看出,本模糊控制器采用了二維模糊調節的方式,以改善系統的動態性能,即模糊控制器的輸入為給定值與測量值偏差e和偏差變化率芿=ek-ek-1所對應的兩個模糊控制集,經量化因子量化后,得到對應的量化等級,其量化等級分別表示為{-7、-6、-5、-4、 -3、-2、-1、0、1、2、3、4、5、6、7}。控制決策表是經離線模糊控制推理運算,并結合系統的實際運行進行調整、修改得到的,但它僅反映常規模糊控制的控制規則,不能保證系統的動、靜態特性在大范圍內最優。因此,為改善模糊控制器的性能,根據系統的誤差和誤差變化等信息,對控制器實行在線調整,實際輸出的控制量為決策表值與比例因子的乘積。比例因子的選取規則如下:當e和芿較大時,系統主要是減少誤差,加快動態過程,應取較大值;當e和芿較小時,系統接近穩定值,應取較小值。最后,按此原則并結合實際經驗得到比例因子表。

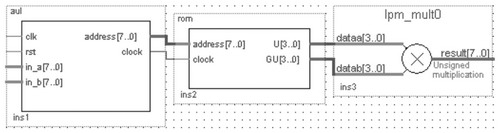

根據上面的分析,利用Verilog HDL語言設計出aul運算模塊和rom存儲模塊,另外由Quartus II軟件的LPM設計乘法器lpm_mult0模塊,如圖3所示。aul模塊首先根據輸入值in_a[7..0]和in_b[7..0]進行求差、除法等運算得到e和芿的值,并乘上各自的量化因子得到量化等級E和艵,然后根據E和艵與控制策略表和比例因子表的對應關系得到查表地址;rom模塊存儲了控制策略表U和比例因子表GU,根據aul模塊傳遞過來的地址查找U和GU表,然后將結果輸出到乘法器模塊,并計算出PWM的調節增量,從而改變PWM的占空比,實現對勵磁電流的調節。

圖3 模糊控制器頂層模塊電路原理圖

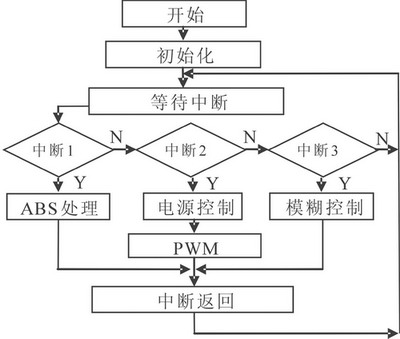

基于Nios的主控程序

Nios處理器是整個系統的中樞,是各控制模塊通訊的橋梁。Nios處理器通過Avalon總線將采集進來的各種參數,如車速、ABS、電壓等,按需要傳遞到各控制模塊,控制模塊再把相關的運算結果返回給主控程序,以實現相關的控制策略,如圖4所示。

圖4 主控程序流程圖

結語

本課題選用Cyclone II系列中的EP2C5Q208C8芯片,它具有4608個邏輯單元,內部RAM達119808位,內部乘法器可達26單元,最大用戶I/O達143個,這些豐富的資源能夠滿足電渦流緩速器控制器各模塊的設計需求,邏輯單元的使用率為65%,RAM使用率為45%。本設計方法提高了系統的集成度和可靠性并且降低了功耗,FPGA的可重構性大大方便了系統將來的升級,而不需要改變原來的電路布線。■