實際案例說明用基于FPGA的原型來測試、驗證和確認IP——如何做到魚與熊掌兼得?

2024-10-31

作者:Philipp Jacobsohn,SmartDV首席應用工程師,Sunil Kumar,SmartDV FPGA設計總監

來源:智權半導體

本系列文章從數字芯片設計項目技術總監的角度出發,介紹了如何將芯片的產品定義與設計和驗證規劃進行結合,詳細講述了在FPGA上使用硅知識產權(IP)內核來開發ASIC原型項目時,必須認真考慮的一些問題。

全文從介紹使用IP核這種預先定制功能電路的必要性開始,通過闡述開發ASIC原型設計時需要考慮到的IP核相關因素,用八個重要主題詳細分享了利用ASIC IP來在FPGA上開發原型驗證系統設計時需要考量的因素。同時還提供了實際案例來對這些話題進行詳細分析。

這八個主題包括:一款原型和最終ASIC實現之間的要求有何不同?當使用FPGA進行原型驗證時會立即想到哪些基本概念?在將專為ASIC而設計的IP核移植到FPGA架構上時通常會遇到哪些困難?為了支持基于FPGA的原型,通常需要對ASIC IP核進行哪些更改?我們如何確保在FPGA上實現所需的性能?在時鐘方面必須加以考量的因素有哪些?如果目標技術是FPGA,而不是ASIC,那么需要如何測試IP核的功能?設計團隊最后還應該牢記什么?

在以往的文章分析了這八個主題之后,最后將通過一個實際案例來回顧前面講到的八項關鍵設計考量因素,并揭示合規性測試、互操作性測和實現方法,以及從不同的方法可能帶來不同的結果與目前非常流行的“視點前移(shift left)”模式相結合來對全文進行總結等精彩內容。

作為全球領先的驗證解決方案和設計IP提供商,SmartDV的產品研發及工程應用團隊具有豐富的設計和驗證經驗。在國產大容量FPGA芯片和IP新品不斷面市,國內RISC-V CPU等IP提供商不斷發展壯大的今天,SmartDV及其中國全資子公司“智權半導體”愿意與國內FPGA芯片開發商、RISC-V IP和其他IP提供商、集成電路設計中心(ICC)合作,共同為國內數字芯片設計公司開發基于本地FPGA的驗證與設計平臺等創新技術與產品。

實際案例:使用基于FPGA的方法來確認USB 3.2 Gen2x1 Device IP

要實現一個可工作的FPGA原型并不是一件容易的事。通常,工程師的想法是使用合適的FPGA邏輯綜合和布局布線(P&R)工具,將已經可用于ASIC技術的IP核映射到足夠大且快速的FPGA上就足夠了,以達到一個功能性FPGA實現。這里的要求是所需的功能應該即刻可用,并且無需進行任何更改。IP核的制造商必須達到這一期望。畢竟,IP核應該能夠集成到現有設計中,且不會有任何重大的時間延遲。假設IP供應商已經提前進行了所有必要的測試,以致于將功能集成到現有電路中毫無困難。

然而對于IP提供商來說,將IP核移植到FPGA架構中是一個具有挑戰性的目標——如果不付出相當大的努力,這幾乎是不可能的。事實是,在沒有適當的基礎架構和外圍設備的情況下,測試一個孤立的IP核只有有限的價值。例如,“獨立”實現并不能保證在符合所有規范的情況下實現所需的功能,特別是在FPGA不僅僅包含孤立IP核的情況下。如果要在FPGA中實現具有高時鐘頻率要求的其他電路部件,這一點尤為重要。

IP制造商面臨的一個特別挑戰是缺乏在后期實現中添加的電路組件的相關信息,如它們的復雜性,它們對時鐘速度的要求等。事實上,一個內核可能已經成功地在與該問題無關的ASIC流片中使用了很多次。畢竟,IP核不僅要滿足標準和規范所定義的所有參數(例如,USB 3.2總線協議規范),而且即使將其集成到一個復雜的整體系統中,該系統被映射到一個可編程器件(即FPGA)上,也仍然要能夠工作。

這樣一個完整系統的復雜性,加上它的所有組件,如微處理器、信號處理電路和接口,對所需的時鐘頻率是否能夠實現以及FPGA提供的資源是否足夠都有重大影響。必須有足夠數量的等效邏輯門,但其他硬件參數也有限制,如存儲器資源、時鐘分布組件、高速IO和/或收發器等。

為了實現可用于在FPGA電路環境中測試IP核的功能性系統,IP核供應商必須考慮的不僅僅是要提供的功能。IP供應商可以接觸到自己創建的功能,但不能接觸到IP核用戶使用的開發和測試環境,也不能訪問連接最終產品的外設,并通過這些外設提供物理輸入信號。同樣,也不能訪問客戶使用的模擬刺激和測試模式生成器。

驗證覆蓋范圍也被視為是至關重要的;在任何可能的情況下,都應該涵蓋極端情況,以避免在使用IP的后續階段出現令人不快的意外情況。值得注意的是測試用的電路板,通常情況下市場可提供的印刷電路板,與IP核客戶隨后將用于所有測試的電路板都有不同。

在輸出端,可以預見到的復雜性并不比輸入信號的供應端更低。以USB接口為例,如果實現接口IP,就需要使用外部PHY作為物理接口。因為這是一個模擬接口,在FPGA上不可用,因此必須使用外部組件。這種PHY由各種各樣的制造商提供,盡管希望將USB控制器連接到由最終客戶選擇的外部PHY組件上,不需要對物理接口進行任何與電氣特性相關的更改,如電壓值、擺幅、輸出引腳的驅動器強度或接口的引腳分配,所有參數都必須在功能測試中進行詳細驗證。

這是確保物理接口符合所有規范的唯一方法,并且數據傳輸的質量也要符合預期。所有這些功能測試都必須提前進行,以保證在交付前的階段就可提供功能。由于IP核必須是通用的,即不同的客戶在不同的應用中選擇PHY來配套都可用,測試設置必須在測試中包括來自不同制造商的許多不同的PHY。

創建數據庫也需要一些工作量。當然,僅僅提供RTL代碼和相應的約束條件是不夠的。為了簡化將IP核集成到現有電路中的工作,通常提供以下數據庫:

Verilog中的RTL設計

RTL能夠在客戶選擇的FPGA邏輯綜合工具上可以進行綜合

具有豁免文件的Lint、CDC和邏輯綜合腳本

Lint、CDC和邏輯綜合報告

如果適用,提供C語音驅動包(裸機驅動)

更詳細的技術文檔

易于使用的、帶有Verilog測試用例的Verilog測試環境

IP測試套件

為最終用戶集成的IP測試臺

用于RTL地址映射的IP-XACT文件

帶有豁免的代碼覆蓋率報告

如果適用,提供IC設計文檔/數據表

USB 3.2 Gen2x1 Device IP:實現、驗證和確認(Validation)

為了確認USB 3.2 IP核,需要對現有IP核進行大量的更改。包括對RTL代碼本身的更改,以及對物理輸入和輸出的微調。對RTL代碼的更改是很有必要的,以使時鐘分布和時鐘生成適應目標FPGA架構。為此,額外的、專用于FPGA的庫組件就被實例化,如所謂的數字鎖相環(MMCM)。

這時也很有必要將數據路徑的總線寬度從32位調整到64位,否則就不可能控制PIPE接口中的時間沖突。由于對PIPE接口的更改,有可能將FPGA中的時鐘頻率從312.5MHz(32位實現)降低到156.25MHz(64位實現),從而使設計適用于目標FPGA目標。最后,FPGA上的布局布線就可以在不存在時間沖突的情況下完成。

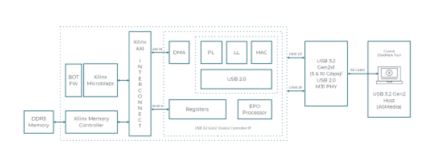

除了上述的設計變更之外,Xilinx / AMD的專有微控制器,即專為該制造商的FPGA開發的Microblaze處理器也被集成到電路中,以執行實驗設置所需的固件代碼。由于USB 3.2 IP核被配置用于大容量存儲應用,因此板載DDR3存儲器被用于外部存儲,該存儲在FPGA本身上不可用,但在選定的原型平臺上可用。USB控制器通過主AXI接口訪問該DDR3存儲器,而USB控制器的核心寄存器由處理器通過AHB從接口訪問。

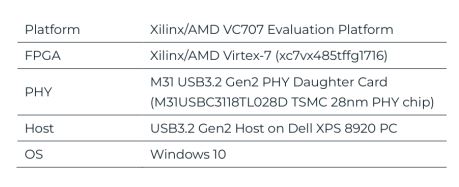

硬件平臺選擇如下配置:

SmartDV USB 3.2 Gen2x1 Device Controller是為USB大容量存儲應用而配置的。它完全符合USB 3.2規范(rev. 1.0)和USB 2.0規范(rev. 1.0)。IP內核有以下接口:

USB 3.2 Gen2物理層接口

-64位PIPE數據路徑

USB 2.0物理層接口

-16位UTMI兼容接口

系統主數據路徑接口

-64位AXI主接口

系統從屬寄存器訪問接口

-32位AHB從屬接口

EPO處理器接口

除了可用于證明電路功能(包括仿真、CDC檢查、linting)正確性而采用的標準化驗證方法之外,還進行了廣泛的測試以確認電路的實現。最后,對IP核進行了認證。為了實現這一目標,USB3.2 Gen2大容量存儲設備進行了USB Implementers Forum, Inc.推薦的多項合規性和互操作性測試,諸如電氣、PHY、鏈路層和強度測試。認證測試是在臺灣的Allion實驗室進行的,這是一家獲得USB-IF認證的機構。SmartDV的器件已與多個第三方主機進行互操作以便進行認證。

具體采用以下方法進行確認:

USB 3.2 Device IP合規性測試

USBCV第9章合規性測試(SSP/SS/HS/FS模式)

鏈路層合規性測試(SSP/SS模式)

所有合規性測試都已成功通過。

USB 3.2 Device IP互操作性測試

與USB.org推薦的ASMedia USB 3.2 Gen2 Host進行互操作驗證

器件列舉測試(采用SSP/SS/HS/FS模式)

連接/分離測試

使用CrystalDiskMark性能基準測試工具,來進行數據傳輸測試(采用SSP/SS/HS/FS模式)

MSC合規性測試

低功耗測試(睡眠/休眠/冷啟動/熱啟動)

金樹(gold tree)互操作性測試(拓撲更改)

所有互操作性測試都已成功通過。

圖1:USB 3.2 Gen2x1 Device IP確認平臺框圖

為了確認USB 3.2 Gen2x1器件的控制器,使用了來自制造商AMD / Xilinx的現成商用的FPGA平臺。物理接口是通過使用來自M31公司的外部PHY卡來實現。

USB 3.2 Gen2x1 Device IP實現挑戰

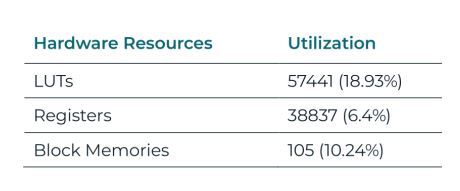

在FPGA中實現USB 3.2控制器絕非易事。由于一些時鐘頻率相當高,時序收斂并不是一件容易的事;它需要對PIPE接口進行設計更改,并需要在FPGA的邏輯綜合(Synopsys Synplify Premier)和Xilinx/AMD Vivado工具布局和布線功能中進行多次迭代。值得注意的是,所選FPGA中的邏輯資源利用率相對較低。

可以假設,在資源利用率較高的情況下,時序收斂會更加困難。基于這一假設,我們注意到市場上在過去一段時間里已經出現了一些功能更強大的FPGA器件,如Xilinx/AMD Virtex Ultrascale+/Kintex Ultrascale+、英特爾Stratix-10或Lattice CertusPro-NX,它們都基于比Xilinx/AMD Virtex-7 FPGA更先進的工藝技術,雖然后者在設計和設置這些測試的時候仍然是被廣泛使用的器件。可以放心地假設,使用這些新一代FPGA器件可以更容易地確保實現所需的時序。

Virtex-7 FPGA(xc7vx485tffg1761-2)的資源利用率如下:

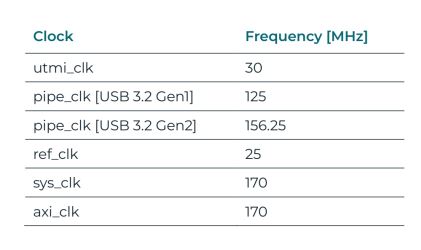

通過調整這兩種工具(Synopsys Synplify Premier和Xilinx/AMD Vivado)的約束和設置,在不違反時間約束的情況下就可能實現。系統中所使用的時鐘域和對應的時鐘頻率如下圖所示:

然而,即使在時序收斂之后,設計也不會立即出現在板卡上。從PHY接收的數據沒有在USB 3.2控制器中正確采樣。因此,有必要部署額外的組件來調整IO延遲值,以便正確地對數據進行采樣。

總的來說,使USB 3.2控制器能夠與外部PHY互操作是一項極具挑戰性的任務。除了解決某些互操作性問題外,還需要開發在Microblaze微控制器上運行所需的固件代碼,以便在大容量存儲應用模式下確認設計。

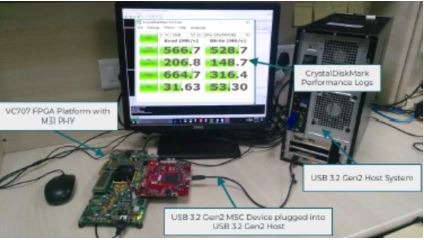

圖2:在SmartDV實驗室中的確認和性能測量設置

電路功能的確認,以及所有互操作性和合規性測試,都是在AMD/Xilinx的標準FPGA板上進行的。此外,測試設置允許我們去確定可實現的數據吞吐量。所有的測試和測量都使用了合適的設備。為了確定可實現的數據吞吐量,我們使用了CrystalDiskMark的性能基準測試工具。

結論:魚與熊掌兼得?

部署可同樣用于ASIC和FPGA架構的IP核是一項極具挑戰性的任務。因此,必須謹慎選擇IP核供應商,并全面詢問其在FPGA實現方面的專業知識。

事實上,即使一款IP核已經經歷了許多次成功的ASIC流片,并在許多芯片產品中得到了使用,但這并不意味著它可以很容易地用于FPGA。相反,盡管FPGA的復雜度通常比硬連線器件低很多,它們至少也需要與ASIC同樣的重視程度。其將花費的努力經常被低估和忽視,特別是在ASIC開發在實現和驗證方面捆綁了所有工程資源的時候。這在很大程度上是因為在有時間壓力的情況下,再加上不斷要求產品能夠盡快進入市場,所以開發ASIC時難以對FPGA等可編程器件給予必要的關注。

事實仍然是,在ASIC驗證中被忽視的錯誤幾乎不可避免地會導致至少需要一次額外的流片,其結果是導致成本大幅增加和項目嚴重延遲,這與流行術語“加快產品上市時間”所描述的完全相反。通過認真地使用FPGA原型,實現“一次流片成功”的概率顯著增加,這會帶來許多優勢,包括產品更早進入市場、研發團隊可以即刻轉向新的項目、項目整體成本得以優化等。

FPGA原型設計增加了驗證覆蓋范圍,并增加了在產品開發的早期階段發現錯誤的可能性,從而減少了在后期必須處理的錯誤。當然,使用預定義的和經過測試的IP核也提供相當大的優勢,因為在這里可以預期更少的意外。通過擴展,最佳的IC設計解決方案則是結合了作為原型設計載體的FPGA和經硅驗證的IP內核,來作為無錯誤實現的保證。使用經過試驗和測試的驗證工具及其所有功能,就可以完成其他工作,從而實現早期目標并成功完成項目。

現在有一個很流行的術語可以形容這種方法:視點前移(shift left)。

最后但同樣重要的一點是,我們必須提到快速完成項目最重要的因素:人。經驗豐富的專家團隊對于電路功能的實現、驗證和確認的價值是不言而喻的——這是最主要的成功因素。對于所有的工具、輔助工具和預定義的電路功能而言,如果你不知道如何高效地組合和使用它們,則它們都是毫無用處的。無論目標是ASIC還是FPGA,擁有強大且可靠的合作伙伴、具有必要專業知識和適當經驗的專家團隊,都是您成功的關鍵。

雖然電路設計從來都不是一件容易的事,但選擇合適的合作伙伴肯定會讓您更輕松。

更多精彩內容歡迎點擊==>>電子技術應用-AET<<