張存生,張德學,韓學森,王超,張恒,冀貞賢

(山東科技大學 電子通信與物理學院,山東 青島 266590)

摘要:直接頻率合成技術(DDS)是無線通信中的關鍵技術,因應用場合及技術指標不同,DDS中的正弦波形產生模塊有多種實現(xiàn)方法,本設計采用CORDIC算法計算波形數(shù)據(jù),并通過預處理實現(xiàn)全部相位波形數(shù)據(jù)的即時計算,不占用存儲資源,且可通過改變迭代次數(shù)來調節(jié)精度。所設計的DDS精度、頻率、相位可調,在Altera Cyclone2中實現(xiàn)時,時鐘頻率可達172 MHz,占用1 171 LUTs。

關鍵詞:FPGA;直接頻率合成技術;CORDIC

中圖分類號:TN99文獻標識碼:ADOI: 10.19358/j.issn.1674-7720.2017.04.018

引用格式:張存生,張德學,韓學森,等.基于CORDIC算法的參數(shù)可調信號源設計[J].微型機與應用,2017,36(4):59-62.

0引言

直接頻率合成技術(Direct Digital Synthesizer,DDS)是電子系統(tǒng)的重要組成部分,也是無線通信中關鍵技術。在數(shù)字混頻中,DDS產生正弦信號與輸入信號進行相乘可以實現(xiàn)信號調制的效果。目前,通過現(xiàn)場可編程門陣列 (Field Programmable Gate Array,F(xiàn)PGA)實現(xiàn)DDS有三種途徑:基于無限沖激響應 (Infinite Impulse Response,IIR)濾波器的實現(xiàn)方法、基于查找表 (Look Up Table,LUT)的實現(xiàn)方法以及基于坐標旋轉數(shù)字計算機 (Coordinate Rotation Digital Computer,CORDIC)算法的實現(xiàn)方法[1]。基于IIR濾波器的實現(xiàn)方法用到大量乘法器,不利于FPGA實現(xiàn),基于查找表的實現(xiàn)方法用到大量ROM資源,而CORDIC算法只需要簡單移位操作和加減操作就可以計算正余弦值,可用FPGA高效實現(xiàn)。CORDIC 算法是一種用于計算一些常用的基本運算函數(shù)和算術操作的循環(huán)迭代算法[2]。

本設計基于CORDIC算法設計DDS,產生正余弦信號,并通過改變輸入信號FWWORD、PH_ADJ_EN、PH_ADJ和DATA_ACC_SEL達到頻率和相位可調以及輸出數(shù)據(jù)精度可調的效果。AD9850芯片可以實現(xiàn)相位的調節(jié),但是其調節(jié)有最小量為11.25°的限制。本設計可以在運行階段將相位在[-180°,180°]之間任意調節(jié),同時可以對數(shù)據(jù)精度和輸出波形頻率進行調節(jié)。用Verilog編寫代碼,使用Modelsim完成代碼仿真,使用Altera的EP2C70F89C6芯片進行資源評估。

1DDS的結構

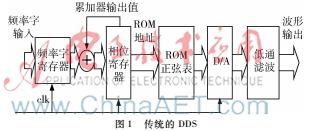

圖1傳統(tǒng)的DDS傳統(tǒng)DDS采取查找表方式進行設計,將相位對應值預先存儲在ROM中,通過地址控制找到相位對應正余弦值,從而產生正余弦波形。這種方式會用到大量ROM資源。傳統(tǒng)DDS設計見圖1。本文基于CORDIC算法設計DDS,通過改變輸入信號FWWORD、PH_ADJ_EN、PH_ADJ和DATA_ACC_SEL實現(xiàn)波形頻率、波形相位和數(shù)據(jù)精度可調,同時不使用ROM資源,其中FWWORD調節(jié)波形頻率、PH_ADJ_EN和PH_ADJ共同調節(jié)相位,DATA_ACC_SEL通過選擇不同迭代次數(shù)的迭代數(shù)據(jù)改變輸出數(shù)據(jù)的精度。

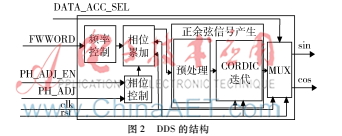

本設計主要包括相位累加、頻率控制、相位控制、CORDIC預處理、CORDIC迭代和迭代次數(shù)選擇模塊,結構如圖2所示。其中通過CORDIC預處理和迭代部分求出每個相位對應正余弦值,并將計算結果輸出。在相位累加部分,通過相位不斷循環(huán)累加獲得[-180o,180o]之間的相位,將累加相位數(shù)據(jù)送到CORDIC算法模塊,進而得到連續(xù)輸出的正余弦函數(shù)值,獲得正交正余弦波形。迭代次數(shù)選擇模塊則可以選擇不同迭代次數(shù)進而改變輸出數(shù)據(jù)的精度。與參考文獻[2]和[3]相比,加入了數(shù)據(jù)精度、波形相位和波形頻率調節(jié)部分。與AD9850芯片相比,相位調節(jié)不再受到限制,并且輸出數(shù)據(jù)精度可以調節(jié)。

2CORDIC算法[1,4]

CORDIC算法可以用來直接計算正余弦函數(shù)、乘除法以及雙曲函數(shù)。經(jīng)過發(fā)展CORDIC算法已經(jīng)發(fā)展成為擁有圓周系統(tǒng)、線性系統(tǒng)和雙曲系統(tǒng)的一個算法系統(tǒng)。每種系統(tǒng)中又包含旋轉模式和向量模式兩種不同的計算模式。本設計采用圓周系統(tǒng)中旋轉模式計算正余弦值,獲得相位對應正余弦值。為了保證數(shù)據(jù)在量化后沒有溢出,CORDIC算法迭代部分輸入信號采用16位有符號數(shù),迭代次數(shù)由DATA_ACC_SEL決定,最多為16次。

2.1算法迭代原理

圓周系統(tǒng)旋轉模式矢量旋轉圖如圖3所示。

根據(jù)圖3可知P點的坐標如下:

xP=cosα

yP=sinα(1)

逆時針旋轉β得到的Q點坐標為:

xQ=cos(α+β)

yQ=sin(α+β)(2)

展開可得:

xQ=cosαcosβ-sinαsinβ

yQ=sinαcosβ+cosαsinβ(3)

將式(1)代入式(3)可得:

xQ=xPcosβ-yPsinβ

yQ=yPcosβ+xPsinβ(4)

提出cosβ可得:

xQ=cosβ(xP-yPtanβ)

yQ=cosβ(yP+xPtanβ)(5)

如果去掉cosβ可以得到R的坐標:

xR=xP-yPtanβ

yR=yP+xPtanβ(6)

將β分成若干次疊加,那么每次的疊加結果與上次的關系為:

xi+1=xi-yitanβi

yi+1=yi+xitanβi(7)

不妨令

βi=tan-1(di2-i)(8)

將式(8)代入式(7)可得:

xi+1=xi-diyi2-i

yi+1=yi+dixi2-i(9)

為了確定di的符號,引入變量Z,并給出如下關系:

zi+1=zi-ditan-12-i(10)

得到圓周系統(tǒng)旋轉模式下的迭代方程如下:

xi+1=xi-diyi2-i

yi+1=yi+dixi2-i

zi+1=zi-ditan-12-i

di=+1,zi≥0

-1,zi<0(11)

式(11)沒有考慮到模長處理。引入模長補償因子An。在圓周系統(tǒng)旋轉模式下,最終迭代的目標是使得Zn=0,最終得到圓周系統(tǒng)旋轉模式公式如下:

![OR]TU)_EJMCF@76X~64__6K.png OR]TU)_EJMCF@76X~64__6K.png](http://files.chinaaet.com/images/2017/03/05/6362434768178295097549635.png)

根據(jù)式(12)和式(13)可知,給定初始值x0和y0,并根據(jù)迭代次數(shù)確定An,利用CORDIC迭代算法,可得Z0對應的正弦值和余弦值。

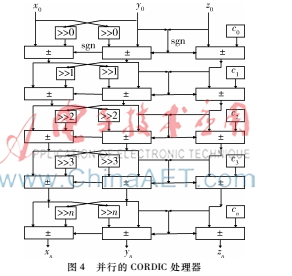

對應式(11)的并行架構設計如圖4所示。參考XILINX CORDIC IP[5]核的設計,本次設計迭代次數(shù)最多為16次,CORDIC迭代模塊是16位有符號數(shù)。

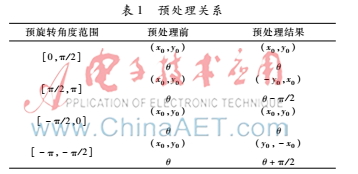

經(jīng)過計算式(8)可以知道β的累加結果在 [-99.88°,99.88°]之間,即可以直接計算角度在[-99.88°,99.88°]之間,不在該范圍內的相位,需要對其進行預處理。

2.2預處理原理

根據(jù)三角函數(shù)的性質,對不能直接計算的相位值進行預處理。CORDIC算法的預處理關系見表1。其中(x0,y0)是預處理之前的坐標,θ是要進行處理的角度。在預處理結果一列中是對應的處理后的結果。引入變量W,根據(jù)預處理對應關系可以得到:

xpre=-σy0

ypre=σx0

Wpre=W0-σ·π/2

σ=sign(z0)(14)

3仿真結果及資源評估

3.1仿真結果

CORDIC迭代模塊輸入采用弧度輸入,并對輸入進行量化處理,擴大214倍,輸出結果也將擴大214倍。通過時鐘驅動相位累加模塊,產生連續(xù)相位。

FWWORD為17位有符號數(shù),數(shù)據(jù)范圍在[-65 536,65 535]之間。PH_ADJ為17位有符號數(shù),相位調節(jié)范圍在[-65 536,65 535]之間,量化后CORDIC模塊的輸入值范圍在[-51 472,51 472]之間,因此,PH_ADJ可以進行[-51 472,51 472]之間的任意相位調節(jié)。DATA_ACC_SEL的位寬是2,可以選擇迭代7次、10次、13次或16次。

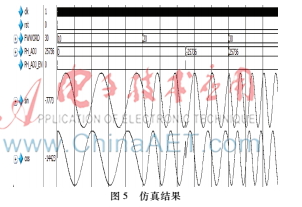

使用Modelsim對設計做仿真,圖5給出了在迭代次數(shù)為16時,對相位和頻率調節(jié)測試的波形。測試開始時頻率累加步長為10,初始相位為0。第一次調整將相位累加步長改為20,相位不做調整。第二次累加步長不做調整,將相位調節(jié)到-90°。第三次將累加步長調節(jié)為30,同時將相位調節(jié)到90°。經(jīng)過三次測試可知,該設計可以產生正交正余弦波形,同時,可以對產生波形的頻率和相位進行調整,并且對單個參數(shù)進行調整時,其他參數(shù)不受影響。FWWORD對頻率進行調節(jié),PH_ADJ_EN和PH_ADJ對相位進行調節(jié),同時相位的調節(jié)不會受到限制。

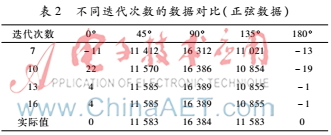

表2給出了在累加步長為10、初始相位為0時,不同迭代次數(shù)產生的數(shù)據(jù)。其中迭代次數(shù)有7次、10次、13次和16次。表中的實際值是真實數(shù)據(jù)擴大214倍之后的數(shù)據(jù)。根據(jù)表中數(shù)據(jù)可知,不同的迭代次數(shù)產生的數(shù)據(jù)精度是不同的,本設計中DATA_ACC_SEL信號可以選擇不同迭代次數(shù)的迭代結果,進而改變數(shù)據(jù)的輸出精度。在13次和16次的迭代中數(shù)據(jù)是一樣的,說明在數(shù)據(jù)位寬一定的情況下,數(shù)據(jù)的最大迭代次數(shù)是一定的。

3.2資源評估

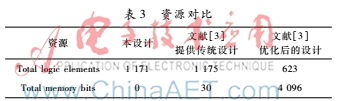

采用Quartus Ⅱ 13設計RTL代碼,并在Altera的EP2C70F89C6 FPGA芯片上實現(xiàn),評估資源利用率和最大工作頻率,與文獻[3]使用的芯片相同。本設計與文獻[3]中的傳統(tǒng)設計及優(yōu)化后的設計資源對比見表3。由表3可知,本設計在加入數(shù)據(jù)精度調節(jié)、相位和頻率調節(jié)后與傳統(tǒng)設計的資源使用[3]相當,且不占用block memory。測得本設計的最大工作頻率可達172.83 MHz高于AD8950的最大工作頻率125 MHz。

4結論

本設計基于CORDIC算法進行DDS設計,對設計進行Modelsim仿真,通過調節(jié)輸入信號FWWORD、PH_ADJ_EN、PH_ADJ和DATA_ACC_SEL能夠達到相位和頻率可調以及輸出數(shù)據(jù)精度可調的效果。

采用Quartus Ⅱ 13設計RTL代碼,并用Altera的EP2C70F89C6 FPGA芯片進行資源評估,在加入數(shù)據(jù)精度調節(jié)、相位和頻率調節(jié)后與傳統(tǒng)設計的資源使用情況相當,并且沒有使用到ROM資源,節(jié)省了ROM資源。

參考文獻

[1] 高亞軍.基于FPGA的數(shù)字信號處理(第二版)[M].北京:電子工業(yè)出版社,2015.

[2] 景標,邢維巍,張燕琴.基于 CORDIC 算法的正交信號源實現(xiàn)[J].現(xiàn)代電子技術,2016,39(7):57-59.

[3] 常柯陽,曾岳南,陳平,等.CORDIC算法在正余弦函數(shù)中的應用及其 FPGA實現(xiàn)[J].計算機工程與應用,2013,49(7):140-143.

[4] 李慶華.通信IC設計(上冊)[M].北京:機械工業(yè)出版社,2016.

[5] 劉東華.Xilinx系列FPGA芯片IP核詳解[M].北京:電子工業(yè)出版社,2013.