馬趙,任尚坤,楊梅芳

(南昌航空大學 無損檢測技術教育部重點實驗室,江西 南昌 330063)

摘要:激勵信號源是電磁超聲檢測系統的核心模塊之一,其輸出信號決定了電磁超聲檢測儀檢測的質量。按照電磁超聲檢測系統對激勵源的要求,設計了相應的正弦脈沖激勵源。該設計系統主要包括FPGA的硬件語言合成脈沖信號、D/A轉換、濾波放大、功率放大和阻抗匹配等硬件電路。該系統可輸出頻率、初始相位、占空比可調的脈沖正弦信號,滿足EMAT對激勵源的要求。可為設計便攜式的電磁超聲檢測儀提供借鑒。

關鍵詞:FPGA;電磁超聲檢測;信號源;硬件電路

中圖分類號:TG115.28文獻標識碼:ADOI: 10.19358/j.issn.16747720.2016.23.024

引用格式:馬趙,任尚坤,楊梅芳. 基于FPGA的電磁超聲脈沖信號發生器的設計[J].微型機與應用,2016,35(23):83-85,89.

0引言

電磁超聲檢測技術(EMAT)是一種新興的無損檢測技術,與傳統的壓電式超聲檢測技術相比具有明顯的優勢。其具有無需耦合劑、非接觸性、能夠在高溫高壓等特殊環境中正常工作等優點,將具有極大的潛在市場價值和廣闊的發展前景[1]。

電磁超聲檢測系統主要由激勵源、EMAT傳感器、接收信號處理系統3部分組成。EMAT傳感器由激勵探頭和接收探頭組成[1]。電磁超聲檢測原理可以概括為:高頻線圈中通過高頻高壓強電流的激勵脈沖信號,在外部偏置磁場作用下,在被測工件的表面或內部產生不同的超聲波。其接收過程與激發過程互為逆過程,接收系統對探頭接收到的回波信號進行處理,輸出到信號顯示端[2]。可以通過對有缺陷的回波信號和無缺陷的回波信號進行觀察分析,來確定缺陷的位置和大小。

目前而言,EMAT還處于研發階段,激勵源的換能效率比較低,導致激發出的超聲波的信噪比較低。高質量的激勵信號源是提高檢測效果的重要保證,本研究的目的是設計制造出高效可靠的電磁超聲激勵源系統[3]。

經過查閱大量相關資料得到,通常采用PWM技術設計脈沖式信號發生器,但該方法輸出激勵信號存在易失真、諧波大、初始相位不穩定等不足。本設計主要采用FPGA技術合成正弦脈沖信號,設計出可靠的脈沖信號發生器。

1硬件電路設計

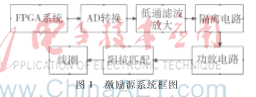

整個硬件系統主要包括FPGA系統、AD轉換電路、低通濾波放大電路、隔離電路、功放電路、阻抗匹配電路等[4],其系統框圖如圖1所示。

(1)FPGA系統

本設計采用了Altera公司的cyclone II系列的EP2C8Q208C7可編程器件。該可編程器件功能強大,I/O端口豐富,輸入時鐘頻率理論上能達到200 MHz。本設計采用輸入時鐘為50 MHz的有源晶振提供系統時鐘信號。另外通過PLL程序設計,提高輸出數字信號的頻率,使之能夠達幾百千赫茲到幾兆赫茲,完全能夠合成滿足條件的脈沖正弦信號。

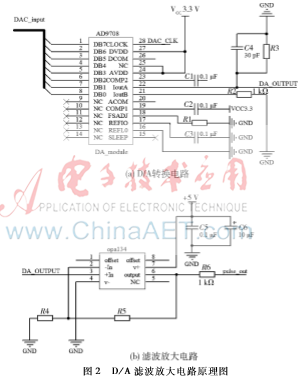

(2)D/A濾波放大電路的設計

在提高FPGA高速輸出數字信號的同時,也需要采用高采樣速度的并行D/A芯片。本設計采用ADI公司的AD9708芯片,它是一種8 bit高速D/A轉換芯片,其最高采樣速度能達到125MS/s,能夠將FPGA并行發出的數字信號轉化為相對應的模擬量。

FPGA 輸出的數字信號經過D/A芯片的轉換,輸出模擬信號,通過低通濾波放大電路進行濾波放大。低通濾波放大電路主要由無源電容電阻并聯濾波電路和放大芯片電路組成,放大芯片采用了OPA134運算放大芯片對濾波后的信號進行運算放大。其設計原理圖如圖2所示。

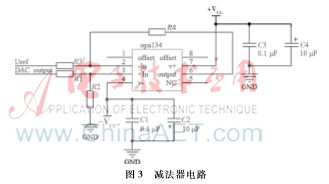

經過運算放大芯片,輸出脈沖正弦信號只有正向電壓。脈沖信號通過減法器電路輸出交流電壓。減法器(Subtracter)同樣采用TI公司的OPA134運算放大芯片,其電路原理圖如圖3所示。

(3)信號功率放大電路設計

EMAT要求輸出的激勵脈沖功率大,需要輸出的脈沖功率達到幾百瓦甚至是幾千瓦。越高的激勵功率越容易在檢測工件內部激勵出超聲波。考慮到輸出信號的功率大,將輸出的脈沖信號先通過1:1的繞線比例變壓器將脈沖發生電路與功放電路進行隔離,從而減小后期的功率放大對信號發生電路產生的影響[3]。

設計采用了集成功放芯片對合成的脈沖信號進行功率放大。采用的集成功放芯片是TDA7293功率放大芯片,能夠有100 W的輸出功率。同時為了使線圈獲得最大的功率,需要對電路進行阻抗匹配設計。

(4)阻抗匹配電路設計

阻抗匹配電路是電磁超聲檢測系統的重要組成部分,阻抗匹配是指負載阻抗與激勵源內部阻抗互相適配,得到最大功率輸出。對于不同特性的電路,匹配條件是不一樣的。對于純電阻而言,電源內阻的大小等于外部電阻的大小,此時外部負載能夠獲得最大的功率;對于阻抗電路而言,其輸入阻抗與輸出阻抗共軛,此時負載能夠獲得最大的功率[3]。

2FPGA激勵源數字系統設計

現場可編程門陣列(FPGA)是一種采用硬件編程語言編程的器件,具有靈活的、可編程的邏輯門陣列芯片。利用硬件描述語言(HDL)能夠完成各種數字電路系統的設計,減少了傳統邏輯門芯片的數量,簡化了硬件電路設計;FPGA器件的時鐘頻率能達到幾十兆甚至幾百兆赫茲,完全能夠滿足合成高頻信號的要求 [5]。

本文主要利用FPGA器件合成所需要的脈沖式正弦信號。由于EMAT需要的激勵信號是脈沖式的,若直接采用DDS芯片作為激勵輸出信號,其輸出的信號是連續的,很難通過硬件控制或者軟件編程,使其輸出的信號呈現脈沖周期性;同樣采用高速開關控制,很難保證信號的周期性。經過多方面考慮,采用FPGA器件,利用硬件編程語言合成脈沖信號。FPGA合成脈沖正弦信號包括兩部分,即 FPGA查找表的設計和Verilog HDL語言編程實現輸出。

2.1FPGA查找表的設計

查找表(LUT)是合成波形的關鍵部分,如何建立查找表至關重要。本設計采用MATLAB軟件工具,編程產生一個周期的正弦波形,并采樣正弦圖像若干個點,提取出相應的點所對應的數值。經過一系列的數字處理,將處理后的數值輸入到quartus II 新建的rom文件中。具體設計如下:

(1)設置正弦波的相關參數。在MATLAB中設置正弦函數的頻率、初始相位、采樣頻率、采樣點數、振幅以及直流分量的值,使MATLAB能夠輸出一個周期的正弦波形。本設計如下:

f=1;Fs=256;P1=0;

N=256;t=[0:1/Fs:N/Fs];

A0=128;A=128;

s=A*sin(2*pi*f*t + pi*P1/180) + A0;

B=round(s);plot(s);

其中f為信號頻率,本設計只需輸出一個周期的波形,即f=1;Fs為采樣頻率,滿足Fs>2f;N為采樣點數;s為函數表達式;B中的值是s四舍五入后的值。

(2)在MATLAB的workspace對話框中提取B的值,輸入到quartusII新建的Memory Initialization File文件中,建立sin.mif文件。其數據格式如圖4所示。

2.2FPGA編程合成信號

現場可編程門陣列(Field Programmable Gate Array,FPGA)是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的。Verilog HDL 硬件描述語言廣泛應用于數字系統設計中,本設計也采用了該硬件描述語言來描述FPGA內部數字系統的設計,從而輸出滿足要求的脈沖信號 [2]。

本設計的核心思想是對Look-up Table讀取地址所對應的數據,通過時鐘控制輸入到D/A芯片的數字端口,轉換成模擬信號。首先在設計模塊中定義出相關的輸入輸出端口,輸入輸出端口主要包括時鐘輸入端CLK、復位輸入端口RST_B、8位數據輸出端q端口、輸出DAC芯片時鐘信號端口。模塊設計端口設置如下:

/***********I/O Port*************/

input CLK;

input RST_B;

outputq;

outputDAC_CLK ;

wireCLK;

wireRST_B;

wire[7:0] q;

wireDAC_CLK;

ROM例化到模塊電路中代碼:

/**********ROMinstance************/

ROM_P I_ROM_P(

. address (addr),

.clock (CLK),

.q(q ));

例化后的mif文件導入到數字模塊中,程序模塊生成數據地址,將地址匹配到ROM_P的地址,從而讀取地址所對應的數值。在硬件層面,通過時鐘信號的控制,將ROM_P中地址對應的數值送到D/A芯片的輸入端,從而轉化成模擬信號,合成所需要的正弦脈沖信號。

3實驗結果

在完成相關設計后,對硬件電路和FPGA數字系統進行相關調試,完成相關的測試。設置相關的參數,利用quartusII軟件平臺,將設計的數字系統下載到硬件系統中。

用數字示波器顯示出單通道正弦脈沖信號的波形,如圖5和6所示。通過FPGA控制調節設置相應的參數, 輸出多脈沖信號波形,如圖7所示。

本設計可以產生可控周期數的正弦脈沖信號,且其脈沖信號的頻率可以通過設置相應的參數來調節,調節范圍可達幾十千赫茲至幾兆赫茲,完全能夠滿足電磁超聲脈沖信號發生器的要求。

4結論

信號發生器是電磁超聲檢測系統的核心組成部分之一,本文設計的脈沖式正弦信號發生器能夠提供較為穩定的正弦脈沖信號。研究結論如下:

(1)采用FPGA芯片,利用硬件編程語言合成脈沖信號,具有頻率高、信號穩定的特點,克服了直接采用DDS芯片作為激勵輸出信號連續性的不足,使輸出的信號由連續式變為脈沖式,并且簡化了模塊電路的設計。

(2)利用FPGA芯片產生脈沖式正弦信號,能夠精確控制高頻脈沖信號輸出,通過功率放大隔離和阻抗匹配,能夠產生適合電磁超聲檢測的激勵信號。該設計克服了采用PWM傳統技術輸出信號易失真、諧波大、初始相位不確定等不足。

參考文獻

[1] 黃松嶺,王坤,趙偉. 電磁超聲導波理論與研究[M]. 北京:清華大學出版社,2013.

[2] 潘偉才. 基于FPGA的電磁超聲檢測系統的研究[D].哈爾濱:哈爾濱工業大學,2008.

[3] MIRKHANI K, CHAGGARES C,MASTERSON C,et al. Optimal design of EMAT transmitters[J]. NDT & E International, 2004, 37(3): 181-193.

[4] 金哲.鋼軌應力的電磁超聲檢測技術研究[D].南京:南京航空航天大學,2011.

[5] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2008.