胡奇宇,陳益民,彭松

(廣東工業大學 信息工程學院,廣東 廣州 510006)

摘要:基于0.18 μm CMOS標準工藝設計了一種低電壓高性能運算放大器。闡述了具有負反饋的三支路基準電流源、帶有正反饋環路增益提高的CMOS源極耦合差分輸入級結構電路。基于頻率補償思想,提出一種新型頻率補償方法,能夠有效提高運算放大器的系統性能。經版圖后仿真表明:該運算放大器在1.2 V電源電壓下具有109 dB的直流增益,259 MHz的增益帶寬,相位裕度74°,功耗為0.82 mW,能夠廣泛應用到大多數電路中。

關鍵詞:低電壓;三支路基準電流源;正反饋環路;前饋補償

中圖分類號:TN432文獻標識碼:ADOI:10.19358/j.issn.1674 7720.2016.23.008

引用格式:胡奇宇,陳益民,彭松. 一種低電壓高性能的運算放大器設計[J].微型機與應用,2016,35(23):28-30.

0引言

運算放大器在實際電子產品設計中是最基本的模塊,隨著電子產品不斷地向便捷式方向發展,對它的電壓要求越來越低,目前在提高低壓運放的性能時,最值得關注的發展動向是對結構的改進[1]。本文在新的框架結構中引入亞閾值工作電路,使差分輸入MOS對管工作于亞閾值區,電路工作在亞閾值狀態時電流很小,以此降低功耗。對輸入級差分對的負載采用交叉耦合帶正反饋的結構,通過增大輸入管的跨導來提高增益。頻率補償使用一種新的前饋技術取代傳統零極點分離帶密勒電容的補償技術。

1運算放大器的電路實現

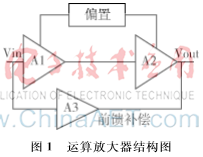

本文所設計的運放電路由偏置模塊、兩級放大模塊、前饋補償電路構成,如圖1所示。其中偏置電路提供基準電流;兩級放大模塊是運放的核心電路;前饋模塊為運放提供一定的增益及頻率補償,使系統穩定。

1.1三支路基準電流源

基準電流源是模擬集成電路中用來為其他電路提供高精度、低溫度系數的電流源,是電路中必不可少的模塊[2]。為了提高供給運放基準電流的電源抑制比(PSRR),使基準電流隨VDD的變化較小,該設計采用三支路基準電流源結構。如圖2所示。

其基準電路由MOS管M1~M6和電阻R構成。該電路在普通基準電流源的基礎上增加一條由M5、M6構成的從電源到電阻R上端后到地的第三條支路,用于形成負反饋。工作原理:當電源電壓正向增加時,ID5的A點電壓升高,使得M2的漏端B處電壓降低,在M1管的作用下,ID1的C點電壓升高,同樣M6作為共源級作用下,使得ID6的A點電壓降低,形成負反饋回路。

為增強其負反饋系統的增益,M6源極與M2源極接在一起后接至產生電壓差的電阻R上端,同樣當電源電壓波動正向增加時M5漏端A處電壓升高,M5、M4管的VSG將會降低,ID5、ID4均減小,由電阻R兩端電壓VR=(ID5+ID4)×R得,電阻R上端電壓降低很快,從而使M5漏端電壓迅速下降,整個電路形成一個更快的負反饋,抑制了電源電壓的變化對系統的影響。

為了使得到的鏡像后的電流IREF的值更精確,在電路中需確保ID3=ID4,即M3與M4的各端電壓要偏置一致。如圖2所示,M5、M4、M3構成電流鏡,M7M9為啟動電路。通過調整M5的漏電流和M6的寬長比,使得VGS6與VGS2相等,由VD1=VD6=VS2+VGS6=VS2+VGS2=VD2得VD3=VD4,因M3、M4源端、柵端都與襯底直接相連,工作狀態一樣,所以得到:

工作在飽和區MOS管的源漏極電流表達式為:

設計中增加了MOS管的柵長,以便忽略溝道長度調制效應。上式中λVDS可以忽略。MOS管在臨界飽和狀態時源漏極電流表達式為:

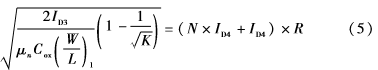

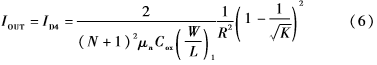

在電路中電阻R產生的源端電壓差VR=(ID5+ID4)×R,初步設計第三支路M5、M6流過的電流為基準電流源的N倍,即ID5=N·ID4,由上式可以得到:

這里令 得:

得:

因此:

由上可知,得到了一個與電源電壓VDD無關的輸出基準電流。由于有兩條支路電流流過電阻R,第三支路M5、M6流過電流是基準電流的N倍,由(6)式可知:N和R均與IOUT成反比,欲得到一個固定輸出的基準電壓IOUT,N增加時,可大大減小電阻R的值,從而節省了芯片layout的面積。(本設計N取4)。

1.2帶正反饋交叉耦合的差分輸入級

在CMOS電路中,電路能夠工作的最低電壓一方面取決于具體電路的結構形式,另一方面則取決于COMS器件的閾值電壓及其過驅動電壓[3]。帶正反饋交叉耦合的差分輸入級電路如圖3所示。

在原有的M3、M4 MOS二極管負載上添加了M5、M6兩個交叉耦合的正反饋負載。從電路中近似看到最小工作電源電壓為1個VTP與3個過驅動電壓之和,采用VTH=0.5 V的MOS工藝,最低工作電壓可降低1 V左右。為保留一定的余度,本設計電源采用1.2 V。

電路中設置差分對管M1、M2工作在亞閾值區,有利于電源電壓的適當降低。通過增加M5、M6,電路輸入跨導為:

式中gm1為M1管的本征跨導,由此可以看到輸入管的跨導增加了一個因數1/(1-gm6/gm3)。利用這種方法增益改善為:

1.3前饋補償

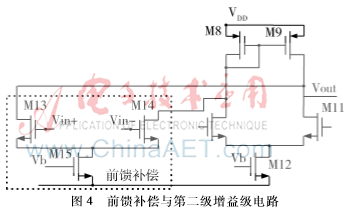

本文在低電壓情況下,使用前饋補償技術取代傳統的主次極點分離密勒電容補償技術。頻率補償是利用前饋路徑在高頻段中引入左半平面的零點正相移抵消極點導致的負相移[5]。由圖4可知,該運放的傳遞函數具有兩個極點和一個左半平面零點,其中ωp1和Z1為:

上式中СO1為第一增益級輸出節點總寄生電容,go為輸出電導,β為反饋因子。

前饋補償與第二級增益級電路如圖4所示。M8~M11為第二放大增益級;M3/M14為前饋級;M12、M17為各自尾電流管。

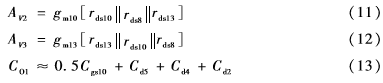

第二級及前饋級(A3)放大器的直流增益,各表達式分別為:

通過調節第二級和前饋級的偏置電流與管子寬長比,使得 確保零點位于左半平面。

確保零點位于左半平面。

2仿真結果

基于0.18 μm CMOS 標準工藝實現運放的版圖照片如圖5所示,在Cadence環境下對運放電路版圖后仿真。在工作電壓1.2 V,驅動2.5 pF電容負載下,其開環增益和相位曲線如圖6所示,該結構能得到增益109 dB,單位增益帶寬259 MHz,相位裕度約為73.8°;圖7為電路共模抑制比曲線,低頻時能達到-80.16 dB。

將本文的性能參數與相關文獻對比,如表1所示。從表中可看出本文通過增加少量的靜態功耗,在整體性能上均有所改善,能夠滿足大多數電路的要求。

3結論

本文在傳統兩級運放的基礎上,結合增益自舉、前饋補償等技術,實現了一種新框架的低電壓高性能CMOS運算放大器。在滿足低功耗條件下,對版圖仿真驗證,能獲得高直流增益和高帶寬,系統在穩定性等方面均有較好的性能。該電路能夠應用于帶隙基準源及各類運算電路中,如加法器、比較器等,具有相當廣闊的應用前景。

參考文獻

[1] 何樂年,王憶.模擬集成電路設計與仿真[M].北京:科學出版社,2008.

[2] WANG R T,HARJANNI R. Partial positive feedback for gain enhancement of low power CMOS OTAs[J].Analog Integrated Circuits and Signal Processing, 1995(8):21-35.

[3] THANDRI B K,SILVA MARTNEZ J. A robust feedforward compensation scheme for multistage operational transconductance amplifiers with no miller capacitors[J].IEEE Journal of SolidState Circuits, 2003, 38(2):237-243.

[4] CHANG Y S,WU H C,SHIAU M S,et al,Pseudo differential operational transconductance amplifier using common mode feed forward and HD3 feed forward[J].International Symposium on Integrated Circuits, 2011,10(11):250-253.

[5] AKBARI M,BIABANIFARD S,ASADI S.Design and analysis of DC gain and transconductance boosted recycling folded cascode OTA[J].AEU International Journal of Electronics and Communications, 2014, 68(11):1047-1052.