文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.044

中文引用格式: 牛少平,史嘉濤,索高華,等. 一種1394總線分析邏輯電路的設計與實現[J].電子技術應用,2016,42(8):175-178.

英文引用格式: Niu Shaoping,Shi Jiatao,Suo Gaohua,et al. Design and implementation of a 1394 bus analysis logic circuit[J].Application of Electronic Technique,2016,42(8):175-178.

0 引言

IEEE 1394總線標準是一種具有高速、靈活和擴展性好的數據傳輸標準,是目前有效的數據傳輸方式之一,廣泛應用于視頻傳輸、工業控制中,也越來越多地應用在航空領域總線系統中。為確保新一代航空1394總線系統和設備功能的正確性、穩定性,需要一個完善的總線測試環境對系統進行充分測試。

本文結合航空1394系統應用研制中遇到的各種情況,從總線系統的相關需求入手,根據總線設備研制規范,提出了一種航空1394總線分析邏輯電路。該邏輯電路可內嵌于1394總線分析設備硬件中,能進行1394總線數據和狀態的監控、分析與存儲,支持發起多種總線行為和發送總線消息數據,可以為航空領域1394總線系統的研制和測試提供有效支持。

1 設計與實現

1.1 硬件結構

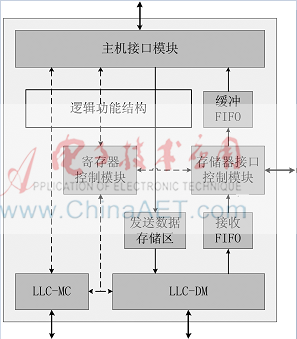

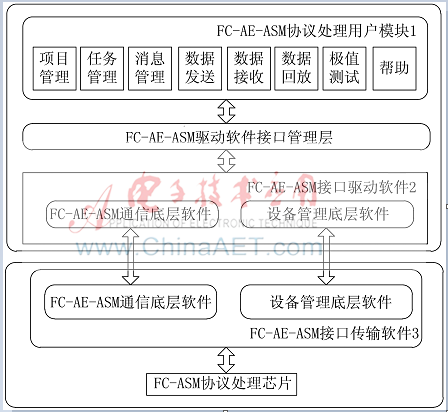

本文提出的1394總線分析邏輯電路內嵌于如圖1所示1394總線分析設備中。其中,外圍硬件主要通過專用芯片實現1394物理層、鏈路層功能、數據存儲功能以及主機接口功能;邏輯電路作為整個設備的功能核心,主要實現總線信息的監控以及解析功能。

圖1 1394總線分析設備結構

1.2 邏輯電路

作為1394總線分析設備的功能核心,分析邏輯電路主要由下面幾個功能模塊組成,其功能結構如圖2所示。

圖2 邏輯功能結構

(1)主機接口控制模塊:實現了邏輯電路與硬件部分主機接口芯片之間的交互功能,包括響應主機發起的命令、解析命令信息,以及將讀取數據進行封包發送等功能。

(2)存儲接口控制模塊:一方面實現對片外存儲器進行數據讀寫的接口功能,將內部提供的數據寫入片外存儲器或從片外存儲器讀取數據;另一方面完成數據信息寫入、讀出操作的調度控制,其工作模式可通過寄存器控制模塊中相應的功能寄存器進行配置更改。

(3)鏈路層接口控制模塊[1]:LLC-DM模塊實現通過鏈路層數據接口進行消息數據收發的功能;LLC-MC模塊實現鏈路層控制寄存器的訪問配置功能。主要完成鏈路層工作模式配置或獲取鏈路層狀態信息等。

(4)寄存器控制模塊:實現用于邏輯功能控制的控制寄存器、用于標識總線狀態的狀態寄存器,以及收發消息的計數寄存器等。初始化、啟動使能、發送幀周期等控制及參數信息均經由主機訪問并操作相關控制寄存器位實現。

(5)其他模塊:包括基于異步FIFO的接收緩沖模塊、基于DPRAM的發送數據存儲模塊,以及不同時鐘域模塊之間的信號同步模塊。

1.3 關鍵設計

1.3.1 存儲結構及存取調度機制

在消息數據和狀態信息的存儲控制方面,采用了如下優化設計:

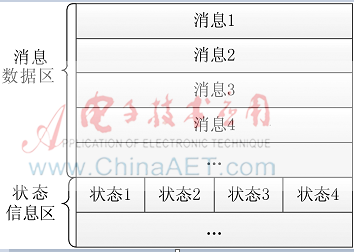

首先,存儲結構。這里將數據信息與狀分析信息進行分區存儲,存儲結構如圖3所示。數據區域按每條消息數據占用2 KB空間劃分,分析信息區域按每條消息占用8 B空間劃分,數據消息與分析信息一一對應。采用這種數據存儲結構,可讓存取操作時的尋址更加規律準確,降低誤操作的概率。

圖3 消息數據存儲結構

其次,存取調度機制。存儲操作時先存數據信息,后存狀態信息;讀取操作時先讀狀態信息,后讀數據信息。存儲調度流程是因為狀態信息是完整分析一條數據信息后才產生的。讀取調度流程是便于軟件從狀態信息開始進行解析。

1.3.2 數據獲取機制

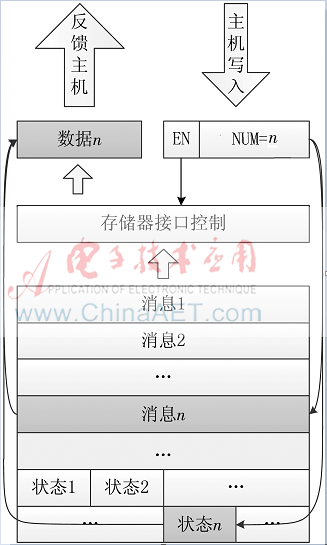

上層主機獲取存儲器中的數據信息時,一般采用直接尋址讀取的方式,而采用這種方式在獲取大量數據時往往需要發起多次多操作,很大程度上影響獲取數據的效率。針對本文設計中的存儲結構,這里采用一種新的數據獲取機制,如圖4所示。

圖4 數據獲取機制

主機以消息條目為輸入,對邏輯內部消息讀取控制寄存器發起一次寫操作,讀取控制寄存器根據指定條目信息直接調度讀取該條信息完整數據并反饋輸出給主機。采用這種機制,主機只需發起一次操作,便可讀取一條消息的數據,這樣一方面可提高數據獲取效率,另一方面提高應用軟件的同步解析效率。

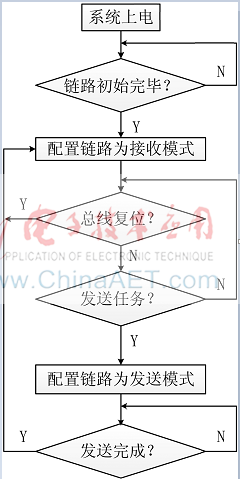

1.3.3 鏈路模式自動配置

1394總線狀態分析需要鏈路工作在正確的模式下,系統上電后,收發消息數據時,鏈路的工作模式就需要進行配置或調整,采用主機直接配置無疑會影響效率,甚至有可能影響正常的總線行為。

針對這種問題,本文在邏輯電路的LLC-MC模塊中實現鏈路工作模式的自動配置機制。如圖5所示,系統上電后,LLC-MC模塊檢測等待鏈路初始化完成后進行默認的接收模式配置。當主機啟動發送任務時,根據鏈路狀態適時配置鏈路切換到發送模式,等待發送完成后再迅速配置切換回接收模式。

圖5 鏈路自動配置過程

2 仿真與測試

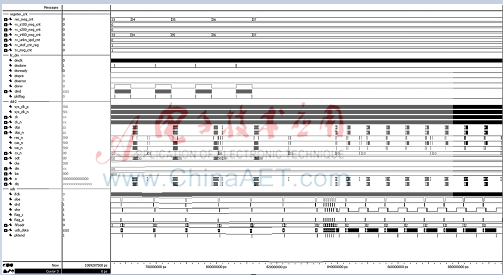

本文首先對1394總線分析邏輯電路功能進行了虛擬仿真驗證。

如圖6所示,鏈路層數據接口llc_dm負責完成消息數據的接收,每接收一條消息,消息記錄計數器rec_cnt_reg計數遞增1,S400速率消息計數器計數遞增1,標識著邏輯電路接收了一條速率為S400的消息數據;llc_dm接口接收完一條消息數據后,存儲器接口DDR2將接收消息數據寫入片外存儲器暫存;最后由主機通過USB接口[2,3]進行數據請求,每請求一次,邏輯通過DDR2接口取出一條消息數據交給USB回傳給主機。

圖6 邏輯功能驗證結果

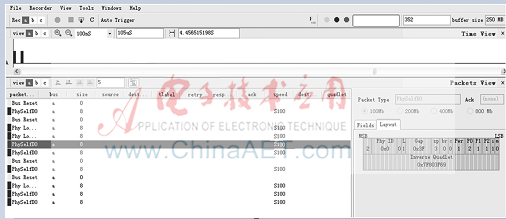

其次,通過嵌入該邏輯電路的1394總線分析設備進行了實踐測試。

如圖7所示,總線分析設備在連接到1394總線系統時,總線復位行為引起了各總線節點設備的響應,分析設備監控到了多次的總線復位行為(Bus Reset)以及各節點發出的S100的物理層自標識消息(PhySelfD0)。

圖7 1394總線分析設備實測結果

由于本文提出的1394總線分析邏輯電路主要針對航空1394總線系統的開發,因而與國內外現有通用1394總線設備相比,其具有更好的適用性、更高的效率以及較低的成本。

3 結論

通過試驗表明,本文所述1394總線分析邏輯電路支持1394總線上不同速率、不同類型的消息數據收發,有效完成總線行為監控和數據分析,同時可內嵌用于多種1394總線仿真設備或用于總線異常分析的測試設備,具有良好的航空系統設備適用性,對于當今航空1394總線系統的研制與開發具有重要的應用價值。

參考文獻

[1] 劉光遠,張濤,鄭偉波.基于FPGA的數據采集系統IEEE1394接口設計[J].儀表技術與傳感器,2009(12):46-48.

[2] Cypress.EZ-USB FX2 Technical reference manual[EB/OL].(2001)[2016].http://www.cypress.com.

[3] 許永和.EZ-USB FX2系列單片機USB外圍設備設計與應用[M].北京:北京航空航天大學出版社,2002.