文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.021

中文引用格式: 王龍,楊承志,吳宏超,等. 基于FPGA的數字基帶多模雷達信號源設計[J].電子技術應用,2016,42(8):87-90.

英文引用格式: Wang Long,Yang Chengzhi,Wu Hongchao,et al. The design of digital multi-mode radar signal generator based on FPGA[J].Application of Electronic Technique,2016,42(8):87-90.

0 引言

隨著雷達技術的快速發展,采用復雜調制樣式、具有低截獲概率(Low Probability of Intercept,LPI)特性的雷達信號被廣泛運用于火力引導和預警探測中,使得傳統電子偵察設備很難截獲到這類信號,需要設計一個能夠模擬這些復雜調制樣式的雷達信號的設備對現有和新研制的電子偵察設備進行測試,檢驗電子偵察設備對LPI雷達信號的有效性和可靠性[1-3];此外,在生成式欺騙干擾中,需要根據偵察到的雷達信號的調制類型和參數產生相應的干擾信號對目標實施欺騙干擾[4,5],因此有必要研究一個能夠靈活產生多種調制樣式的多模雷達信號源。文獻[2]中提出一種采用ARM輸入雷達參數,并通過USB接口將數據傳輸到DSP中進行參數處理,然后傳遞給FPGA合成多種模式的雷達信號的方法,但這種產生多模雷達信號的方法具有整體結構復雜、占用資源多、不利于小型化的缺點。本文設計了一種基于FPGA的多模雷達信號源產生結構,在FPGA中構建微控制器實現參數的處理,降低系統的復雜度,提高了系統的集成度。

本文選用Xilinx Zynq-7 系列xc7z010clg400 FPGA芯片[6]實現系統設計,上位機通過網口向FPGA中構建的微控制器(MCU)發送信號描述參數,微控制器經過計算和處理得到寄存器配置參數,并通過AXI(Advanced eXtensible Interface)總線[7]對自制的多模信號源IP核進行配置,產生特定調制形式和特定參數的雷達信號。由于整個數字系統都在一片FPGA上實現,降低了外部電路的設計難度,易于實現系統的小型化設計,同時關鍵的多模信號源產生模塊被封裝成具有AXI總線結構的IP核,提高了模塊的靈活性、易用性和重用性,通過AXI總線可以很方便地與微控制器連接實現,并且在AXI總線上掛載多個多模雷達信號源IP核,可以模擬多部雷達信號,為電子偵察設備對同時到達信號的性能檢測和生成式同時多目標干擾提供硬件支持。經測試,該IP核最高可工作在500 MHz 的時鐘頻率下,即數字信號的輸出速率能達500 MS/s。輸出的信號調制形式包含常規脈沖信號、線性調頻信號、相位編碼信號、頻率捷變信號、重頻抖動信號、重頻參差信號和其他復合調制信號等。

1 關鍵技術研究

1.1 雷達信號模型

雷達信號的一般表達式可以用下式表示:

其中,A(t)表示信號的時域包絡,f(t)為信號的頻率調制函數, 為信號的相位偏移調制函數。從式中可以看出,雷達信號的調制方式不外乎幅度調制、頻率調制、相位調制、時間調制這四種方式及這四種調制方式的組合,其中幅度調制常見的是矩形脈沖調制,故本文不對脈沖調制作過多研究。

為信號的相位偏移調制函數。從式中可以看出,雷達信號的調制方式不外乎幅度調制、頻率調制、相位調制、時間調制這四種方式及這四種調制方式的組合,其中幅度調制常見的是矩形脈沖調制,故本文不對脈沖調制作過多研究。

以線性調頻信號為例,線性調頻信號是信號的瞬時頻率隨時間線性變化的信號,其瞬時頻率可以用式(2)表示:

其中,f0為信號的初始頻率,K=B/T是信號的調頻斜率。

1.2 DDS原理和模塊設計

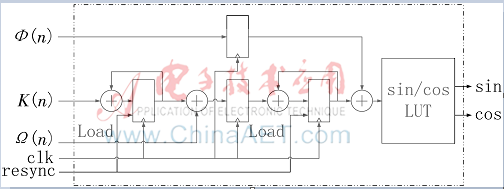

數字頻率合成器DDS(Direct Digital Synthesizer)常用于數字信號產生,主要包括相位累加器和正弦計算器兩部分,其中正弦計算多采用查表的方法實現。DDS技術同模擬方法相比,具有穩定可靠、波形產生靈活、精確度高的優點,因此得到了廣泛應用[8]。本文根據生成線性調頻信號的需求,設計了如圖1所示的二階相位累加結構。雷達信號的通用表達式作離散化,可用式(3)表示:

圖1 DDS模塊結構原理框圖

其中K(n)為時刻的調頻斜率, 為時刻的頻率偏移,

為時刻的頻率偏移, 為時刻的相位偏移。通過控制這三個量,即可輸出單載頻信號、線性調頻和相位編碼等信號調制形式。為了減少查找表對FPGA中RAM資源的消耗,本文采用相位抖動和平衡DAC方法[9,10]對DDS 結構進行改進,抑制了相位截斷誤差并減小DAC非理想特性的影響,仿真結果表明采用該方法能夠有效節約73%的RAM資源。

為時刻的相位偏移。通過控制這三個量,即可輸出單載頻信號、線性調頻和相位編碼等信號調制形式。為了減少查找表對FPGA中RAM資源的消耗,本文采用相位抖動和平衡DAC方法[9,10]對DDS 結構進行改進,抑制了相位截斷誤差并減小DAC非理想特性的影響,仿真結果表明采用該方法能夠有效節約73%的RAM資源。

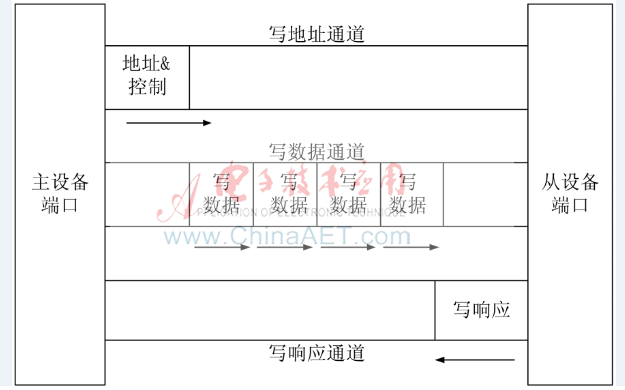

1.3 AXI總線協議

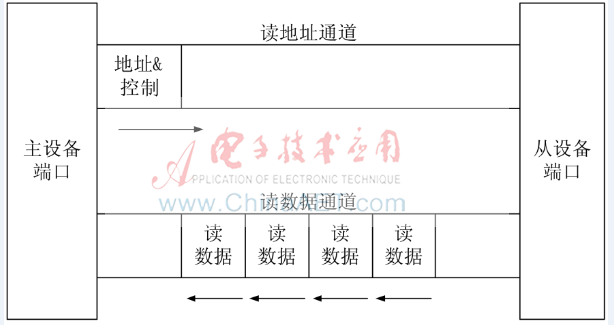

AXI總線是ARM公司提出的一種片內總線協議,該協議是先進微控制器總線結構(Advanced Microcontroller Bus Architecture,AMBA)協議[7]中最重要的部分,面向高性能、高帶寬、低延遲的片內總線。Xilinx公司提供的IP核基本都采用這種總線結構,顯著提高了系統設計的效率,降低了系統開發的復雜度。為了增強多模雷達信號源模塊的靈活性和重用性,本文將多模雷達信號源模塊分裝成具有AXI總線結構的IP核。圖2為AXI總線讀寫通道結構。

(a)AXI總線讀通道結構

(b)AXI總線寫通道結構

圖2 AXI總線讀寫通道結構

AXI總線的地址、控制和數據相互是分離的,支持非對齊的數據傳輸,同時在猝發傳輸中,只需要首地址,同時具有獨立的讀寫數據通道并支持亂序訪問,能更加容易進行時序收斂。AXI 是AMBA 中一個新的高性能協議,并且兼容原有的AHB和APB總線,使得基于原有總線結構的組件能夠很好地與AXI總線結構結合使用。AXI 技術豐富了現有的AMBA 標準內容,滿足超高性能和復雜的片上系統(SoC)設計的需求。

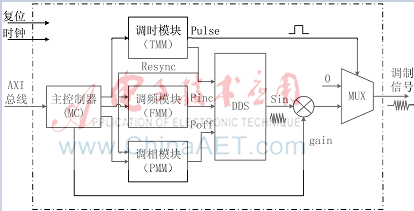

2 多模信號源IP核設計

本文將所設計的多樣式雷達信號源分成時間調制模塊(Timing Modulation Module,TMM)、頻率調制模塊(Fre-quency Modulation Module,FMM)和相位調制模塊(Phase Modulation Module,PMM)3種調制模塊,每個模塊分別負責產生時域調制控制信號、頻域調制控制信號和相位調制控制信號。IP核的頂層結構如圖3所示。

圖3 多模信號源IP核結構框圖

其中主控制器包含所有信號樣式的配置參數寄存器和控制寄存器,MCU通過AXI總線將配置參數寫入到配置寄存器中,并通過讀寫控制寄存器實現對信號源的發射使能、復位等控制。調時模塊TMM產生單比特脈沖控制多路選擇器(MUX)在高電平期間選擇DDS 模塊的信號輸出,而在低電平期間選擇“0”輸出,同時產生同步信號(Resync)給調頻模塊FMM、調相模塊PMM和DDS模塊控制模塊的同步。調頻模塊產生相位增量值(Phase Increase,Pinc)控制信號的瞬時頻率產生調頻類信號。調相模塊產生相位偏移值(Phase Offset,Poff)控制DDS模塊輸出信號的瞬時相位偏移值,產生調相類信號。DDS模塊是信號的產生單元,在調時模塊、調頻模塊和調相模塊的控制下產生特定調制類型的連續信號,經乘法器按指定衰減量衰減后,通過多路選擇器產生具有調時特征的信號,然后輸出特定樣式的雷達信號。

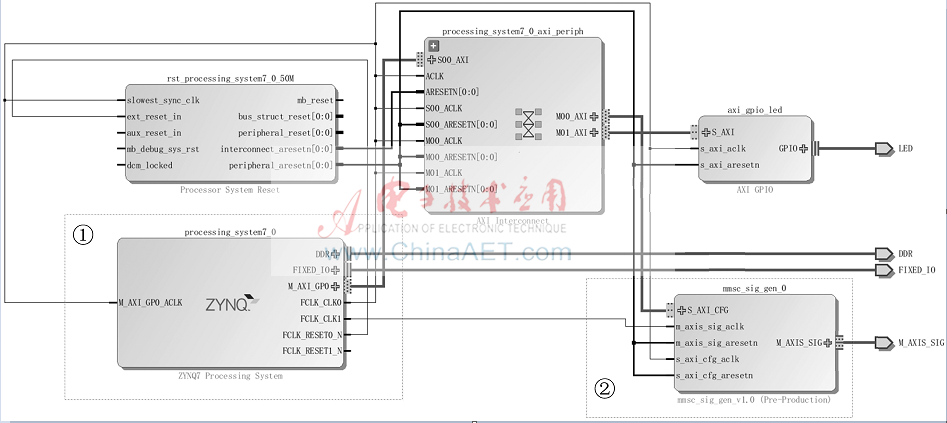

3 多模基帶雷達信號源總體結構設計

多模基帶雷達信號源總體設計結構如圖4所示。上位機軟件通過網口發送信號描述參數給FPGA中的微控制器,微控制器通過計算和處理將信號描述參數轉換為多模雷達信號源IP核需要的寄存器配置參數,然后多模雷達信號源IP核產生數字雷達信號并通過DAC輸出模擬基帶雷達信號。

在Xilinx提供的Vivado編程開發環境中,利用塊設計方式搭建FPGA上的系統結構,最終得到的塊設計圖如圖5所示。其中①為cortex-A9硬核,負責與上位機的網口通信,接收上位機下發的信號描述參數并通過計算處理產生多模雷達信號源IP核所需的配置寄存器參數。②為本文所設計的多模雷達信號源IP核,在cortex-A9硬核的控制下生成相應的基帶雷達信號。

圖4 多模基帶雷達信號源總體結構框圖

圖5 多模基帶雷達信號源塊設計視圖

4 測試與分析

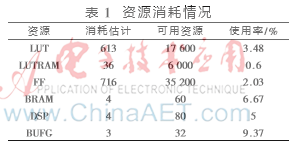

本文在Xilinx公司提供的FPGA開發環境Vivado 2015.4[11]下使用Verilog 語言進行編程,將關鍵的多模信號源模塊分裝成具有AXI總線結構的IP核,使得模塊可以方便地掛載到AXI總線系統中。將系統工作時鐘約束到500 MHz ,進行綜合實現,布局布線的結果表明系統能夠滿足500 MHz 時鐘的時序要求,并且占用資源少。其中多模信號源IP核僅占用了4個DSP核和2個BRAM(Block RAM),分別占總資源的3.3%和5%。具體資源消耗見表1。

將多模雷達信號源的系統工作時鐘設置為250 MHz,信號模式設置為線性調頻脈沖信號。信號的具體參數如表 2所示。

5 結論

多模雷達信號源在電子偵察設備的檢測和生成式干擾信號生成方面具有重要的應用價值。本文提出的基于FPGA的多模雷達信號源具有占用資源少、結構簡單、生成信號多樣的特點,能夠產生常見的調時、調頻和調相信號以及這些調制方法的組合。最高輸出信號的數據速率為500 MHz。

參考文獻

[1] 吳宇,顧村鋒,趙學州.低成本多通道注入式雷達信號模擬源設計方法[J].艦船電子工程,2016(2):58-60.

[2] 史高,胡兆峰.基于BF533和FPGA的雷達信號模擬器設計實現[J].電子科技,2015(1):32-35.

[3] 李楊.多模式軟件化雷達波形產生的技術研究[D].成都:電子科技大學,2013.

[4] 何亮,李煒,郭承軍.生成式欺騙干擾研究[J].計算機應用研究,2016(8).

[5] 馬克,孫迅,聶裕平.GPS生成式欺騙干擾關鍵技術[J].航天電子對抗,2014(6):24-26.

[6] Xilinx Corporation.Zynq-7000 All Programmable SoC Overview[EB/OL].(2016-01).http://www.xilinx.com/support/docu mentation/data_sheets/ds190-Zynq-7000-Overview.pdf.

[7] ARM Corporation.AMBA AXI Protocol(Version:2.0) Speci-fication.[EB/OL](2010-3-3).http://www.arm.com/products/system-ip/amba- specification.php.

[8] 顧趙宇,王平,傅其詳.一種基于DDS的信號源的設計與實現[J].現代電子技術,2015,38(5):51-53.

[9] 王碩,馬永奎,高玉龍,等.基于FPGA的改進結構的DDS設計與實現[J].微電子技術,2016(3):28-30.

[10] Xilinx Corporation.LogiCORE IP DDS Compiler v6_0[EB/OL].(2013-11-18).http://www.xilinx.com/support/docu-menta-tion/ip_documentation/pg141-dds-compiler.pdf.

[11] Xilinx Corporation.Vivado Design Suite User Guide:Designing with IP.[EB/OL](2014-5-1).http://www.xilinx.com/support/documentation/sw_manuals/ug896-vivado-ip.pdf.