王水魚,李艷婷

(西安理工大學 自動化與信息工程學院,陜西 西安 710048)

摘要:本文主要從視頻圖像采集系統出發,針對基于FPGA視頻采集系統中需要實時顯示和高效存儲視頻數據的問題,設計了視頻解碼和SDRAM存儲模塊。在整個系統中使用CCD攝像頭將采集到的模擬信號經解碼芯片ADV7181B解碼后,轉換為數字信號,并使用乒乓存儲方法存儲在SDRAM中,以方便提供給后期其他操作。在分析了視頻解碼及SDRAM的基本原理和主要參數的基礎上,利用Verilog語言實現了將有效視頻數據分離出來并串行輸出,同時也將圖像分辨率調整為符合VGA顯示的像素大小。另一方面通過乒乓緩存也保證了實時性、高速度的數據存儲。最后,經過Modelsim仿真驗證,證明了本設計的有效性。

關鍵詞:視頻解碼;ITU-656;SDRAM;乒乓緩存

0引言

圖1視頻采集系統框圖視頻圖像采集系統應用非常廣泛,隨著計算機通信技術的不斷發展,FPGA以其高性能、低開發成本等優點廣泛應用于視頻和圖像處理領域[1],因此,更加深入地研究基于FPGA的實時圖像采集系統, 對于視頻監控系統、高性能的圖像處理等都具有極其重要的作用。本文主要研究的內容是基于FPGA的視頻采集及顯示系統中的視頻解碼和視頻數據存儲的問題,對于提取有效視頻數據流和高效實時存儲大量數據具有顯著性的意義。

1視頻圖像數據采集系統的總體架構

圖1為視頻圖像采集的系統框圖,主要由I2C配置模塊、ITU656視頻解碼模塊、SDRAM控制器模塊、視頻格式轉化模塊和VGA控制器模塊組成[2]。為了使視頻數據能實時、高速的顯示,視頻解碼模塊和SDRAM控制模塊就顯得尤為重要。

2ITU-656解碼

ITU-656是國際電信聯盟制成的視頻標準,是國際電信聯盟建議為實現在專業視頻設備之間傳輸BT.601標準、4∶2∶2的YCrCb數字視頻信號而定義的一個并行接口和一個串行接口。其中,并行接口在傳輸4∶2∶2的YCrCb視頻數據流的同時,也會輸出水平同步信號HS及垂直同步信號VS控制。

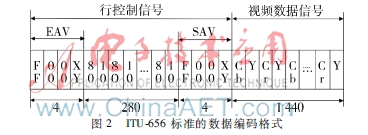

本文中ITU656標準的視頻數據以27 MB/s的速率按Cb,Y, Cr,Y, Cb,Y, Cr,…的順序分時傳送[3]。其中,Cb,Y,Cr是同一個地址的亮度和色差信號,Y對應于下一個亮度采樣信號。 Y采樣頻率為13.5 MHz,Cb采樣頻率是6.75 MHz,使用8位PCM編碼表示每個采樣點。ITU656 標準的數據傳輸格式如圖2所示,每行采樣1 728個樣本點,其中Y為720個,Cb,Cr各360個。消隱期間的數據為288個(包括EAV和SAV)。

行控制信號有兩個定時基準信號:SAV和EAV。 EAV和SAV之間有280個固定填充數據。 SAV和EAV具有相同的前同步碼:FF,00,00,而后面的XY決定著該行在整個數據幀的位置,并且SAV和EAV信號可以通過XY的值來區別,同時XY也包含有奇偶場識別、狀態和信息、場消隱行消隱狀態。

F:F=0奇場,F=1偶場;V:V=1消隱數據,V=0有效行數據;H:H=0表示SAV,H=1表示EAV;P3,P2,P1,P0:保護比特位,其值由F、V、H 決定。

ITU656數字解碼模塊[4]的功能是根據ITU656視頻數據流的特點將有效視頻數據YCbCr和F、V、H 控制信號分離開來,并通過計算像素行列的坐標,確定圖像中像素的具體位置,根據ITU656數據傳輸時序,通過行內計數方式去除行消隱數據,并分離出SAV、EAV 信號,留下只包括YCbCr信號的數據流,并將其串行輸出。ITU656數字解碼模塊另一個功能是通過計算水平數據的像素坐標,將圖像分辨率由720×576調整為640×480,以便在VGA中顯示。

根據SAV 和EAV 都是以FF、00、00 的順序開始的特點,設置一個序列移位器,采用4級寄存器級聯的形式,每個寄存器緩存8 bit數據,并監測后面3個寄存器的值,當這三個寄存器緩存的數據不是FF、00、00時,序列移位器向右移,當檢測到這3個寄存器的值為FF、00、00、時,即認為是SAV或EAV的到來,就將第一個寄存器的 bit6、bit5、bit4分別存放到3個一位寄存器中,從而提取出 F、V、H 信號。H(bit4)如果為0,即表示有效數據開始。再通過 V、F是否為0可判斷出是有效行數據還是消隱數據,是奇場還是偶場的數據。解碼過程如圖3所示。

調整圖像分辨率,定義一個Active_Vedio信號,如果Active_Vedio在0~1 440之間,則為有效視頻數據。首先720行數據調整為640行數據,把SAV和EAV信號提取出來后,此處設計一個FVAL信號,如果FVAL為1,則得到一行720個有效像素值,因此要在這720個有效像素中裁剪掉80個像素。本設計使用Verilog語言,水平方向的像素提取用一個除法器iskip來實現,定義一個水平計數器OTY_X,即除法器iskip=OTV_X%9,若iskip為0,則該像素點被丟棄,否則保留。在丟棄像素點時遵循兩個原則[5]:(1)像素數據為只包含亮度信息的像素點,則將此像素點的亮度值Y丟棄,并且將上一個像素點的色度分量Cr同時丟棄;(2)像素數據為一個完整的像素點,包含了Y、Cb、Cr分量值:將分量Y和Cb丟棄,保留Cr;其次576行數據調整為480行數據,根據PAL制式視頻信號的特點,分別取偶數場24~264行240個數據,奇數場312~552行240個數據,組成480行VGA數據,其他數據丟棄,由于丟棄的僅是一副圖像的最邊緣部分,所以對整幅圖像影響不大。

提取有效視頻數據,PAL制式的視頻信號的場消隱一共是49行,其中偶數場和奇數場的消隱期分別為24行和25行。通過設計一個4位行計數器TY_Y實現,當Hs=1時對Vs進行計數,如果YV_Y大于或等于24,就可以輸出穩定的有效視頻數據。

解碼模塊如圖4所示。

圖5是ITU656 數字解碼模塊在Modelism6.6中的仿真圖,圖中TD_DATA是輸入的視頻流,當它出現FF0000同時XY中的H、V 都為0時,開始輸出有效的視頻數據,輸出信號oYCbCr的高8 位為Y,低8位為Cb和Cr交替出現。

3SDRAM控制器設計

視頻采集模塊中,采用ITU656同步時鐘27 MHz,而SDRAM的工作時鐘通常在100 MHz以上。為解決讀寫時鐘不同步的問題,本設計中,采用了四個異步FIFO[6]用于跨時鐘域的同步化,其作用是將CCD攝像頭采集進來的圖像數據進行緩存,通過寫FIFO讀入SDRAM,讀FIFO輸出給VGA控制器。讀寫FIFO是利用FPGA的片上資源從IP核中調用過來的,將SDRAM的數據端口仿真成四個虛擬端口(兩個寫端口兩個讀端口),控制器根據緩存FIFO的狀態對SDRAM發出讀寫請求,采用頁模式突發傳輸和Bank切換的方式來匹配時序要求。

異步FIFO的宏模塊設計如圖6所示。

圖6FIFO宏模塊 SDRAM 本身要進行刷新、預充電等操作,不能時刻處于傳輸數據的狀態,而且控制邏輯比較復雜,不能和其他器件進行透明連接,為此,設計一個 SDRAM控制器,其他模塊就可通過 SDRAM控制器模塊接口和 SDRAM 相連接,從而對 SDRAM 進行操作,實現乒乓緩存。

本文設計的SDRAM控制器[7]主要由系統讀寫控制模塊、SDRAM控制接口模塊、命令解析響應模塊、數據通道模塊組成,其內部結構如圖7所示。

(1)系統讀寫控制模塊

該模塊的功能是與外設接口相連,接受外部發來的控制信號,并對控制信號進行編碼。根據FIFO的空滿狀態發出對SDRAM的讀寫請求信號。當寫FIFO里面所存儲的數據大小為SDRAM一頁數據時,則寫FIFO通過讀請求信號往SDRAM里面傳輸數據。因為每個端口FIFO里面可以緩存兩頁大小的SDRAM數據,所以當寫FIFO向SDRAM里面傳輸數據時也可以繼續緩存輸入進來的圖像數據。同理,當VGA控制器向讀FIFO讀取數據時,讀FIFO里面緩存的數據大小小于SDRAM每頁的大小時就可以進行讀出了,此時SDRAM也可以繼續向讀 FIFO里面緩存數據。以此輪流進行緩存操作。

(2)SDRAM 控制接口模塊

該模塊主要完成初始化功能以及分析系統指令。初始化結束后,系統開始接收并分析指令信號和地址信息,同時還要分析來自命令模塊的CMD_ACK反饋信號,并產生相應的SADDR信息給命令響應模塊。

(3)命令解析響應模塊

該模塊接受來自SDRAM控制接口模塊的指令并進行判斷,根據發來的指令產生對SDRAM進行控制的信號:地址信號(ADDR)、控制信號(CS、CKE)和指令信號(RAS、CAS、WE)。此外,可以通過LOAD-MODE命令,對預設的模式寄存器進行配置,從而實現對SDRAM工作模式的操控。最后,該模塊通過使能信號OE來判斷讀、寫請求信號,以此來控制數據通路模塊數據的發送方向。

(4)數據通路模塊

數據通路模塊的功能是:在寫數據時將輸入的數據送入到SDRAM中或者在讀數據時將SDRAM中的數據送到數據輸出口。

SDRAM控制器的頂層模塊如圖8所示。

設計好 SDRAM控制器后,采用2個SDRAM,利用乒乓緩存[8]結構的方式來實現對視頻信號的緩存。在第1個緩存周期,輸入的數據流在SDRAM控制器控制下被寫入到SDRAM1中。在第2個緩存周期,通過選擇信號的切換,將輸入的數據流寫入到SDRAM2中;同時,將SDRAM1中寫入的第1個緩存周期的數據讀出,輸出到運算處理單元進行處理。在第3個緩存周期,再次通過選擇信號切換數據的輸入與輸出緩存單元。如此循環,從而將緩沖的數據流不停頓地送到下一模塊進行處理。

圖9為SDRAM控制接口模塊的時序仿真圖。圖中,完成初始化后,該模塊根據CMD指令,解析出對應的SDRAM操作命令。

圖10是指令解析響應模塊仿真時序圖,該模塊根據發來的讀、寫、刷等命令,對SDRAM的控制信號RAS_N、CAS_N、WE_N、CKE進行編碼。

4結論

本文首先介紹了基于FPGA視頻采集系統的整體設計,對于采集和存儲過程中實時性和高效性的要求,分別討論了ITU656視頻解碼中需要從采集到的視頻數據中提取出有效視頻數據流,以及將其調整為符合VGA顯示的像素大小。在存儲模塊中,SDRAM的工作時鐘和視頻采集系統的時鐘不同,為解決讀寫時鐘不同步的問題,采用異步FIFO實現跨時鐘域的同步化,同時采用了兩片SDRAM實現乒乓緩存設計,對SDRAM控制器各個模塊分別進行Modelsim仿真驗證,得出正確結果,可以滿足系統的整體要求。

參考文獻

[1] 馬峰,徐和根,趙曼,等.基于FPGA的智能卡控制器的實現[J].微型機與應用,2013,32(1):2022.

[2] 沙晶晶.基于CPLD的VGA時序彩色信號的實現[J].微型機與應用,2013,32(1):5758,61.

[3]范興山,彭軍,黃樂天,等.基于OpenCL的FPGA設計優化方法研究[J].電子技術應用,2014,40(1):1619.

[4] 趙清華.基于FPGA的目標跟蹤算法的設計與實現[D].西安:中國科學院西安光學精密機械研究所,2014.

[5] 祝長鋒,肖鐵軍.基于FPGA的實時圖像檢測技術的研究[D].鎮江:江蘇大學,2008.

[6] 占文慶.基于FPGA的視頻監控系統的設計[D].武漢:武漢理工大學,2014.

[7] 何云斌,張玉芬.多端口SDRAM控制器的設計與實現[D].哈爾濱:哈爾濱理工大學,2009.

[8] 黃彪.基于FPGA的高清視頻信號實時處理系統的研究[D].西安:國科學院西安光學精密機械研究所,2013.