文獻標識碼: A

文章編號: 0258-7998(2015)04-0029-03

0 引言

PCM(Pulse Code Modulation)是一種有效成熟的數字化的編碼系統,廣泛應用于航空、航天、地面遙測站、移動遙測試驗等國防領域中[1-3]。數據綜合器是彈上遙測設備的數據綜合設備,不同型號導彈根據測試參數數量的不同配置不同數量的數據綜合器,分布在導彈的彈頭、彈體及彈尾。數據綜合器控制彈上各種采編器、中間變換器。各采編器采集到的參數經中間變換器變換后發送到內部數據總線上,數據綜合器在時序的配合下,接收這些數據并按照預先約定的幀結構進行編幀,之后以綜合數據流的形式輸出給遙測發射機進行調制和功率變換。由于應用場合的特殊性,數據綜合器通常不具有通用性。不同的數據綜合器通常具有不同的碼型、碼率、幀格式、接口。研制一種碼率、碼型、幀格式、位寬等可以柔性調整的通用數據綜合器測試儀,可以在保證測量效果的前提下,實現不同產品復用一臺測試儀,從而提高可靠性,降低研發成本,加快遙測系統研制配套周期[4-5]。

1 系統總體結構

測試系統硬件采用總線背板與模塊化插卡方法,如圖1所示,主要由背板總線模塊、主控模塊、綜合數據流測試模塊、模擬源模塊及電源模塊組成。上位機使用LabWindows/CVI 編寫,該軟件是建立監控檢測系統,自動化測試環境與數據采集系統的理想開發環境。

測控計算機配置各模塊的相關參數,包括碼型、碼率、幀同步碼、幀長,并對測試儀解碼后上傳的數據進行分析、處理及顯示處理結果;主控模塊是整個測試儀的核心控制模塊,上位機下傳的數據和命令以及其他模塊上傳數據都受主控模塊的控制;背板總線是主控模塊與各功能模塊之間的通信橋梁,電源模塊也通過背板總線向測試儀內部各模塊供電;綜合數據流測試模塊接收不同的待測數據流并進行解碼,然后上傳到上位機進行后續處理,是實現通用測試功能的核心;綜合數據流模擬源模塊由上位機配置數據流參數,輸出不同的數據流,用作系統自檢,同時可作為其他外部設備的標準源。

2 主控模塊

主控模塊是聯系測控計算機與測試儀的關鍵節點。與上位機之間的通信通過USB接口實現,與其他各模塊之間則通過高速LVDS總線進行通信。主控模塊電路方案如圖2所示,通過USB接口電路接收上位機下發的命令和數據,由FPGA進行數據格式變換后,在120 MHz時鐘控制下,通過LVDS模塊DS92LV18進行串化后發送至背板總線,總線上的其他模塊按地址接收數據并響應。綜合數據流測試模塊對接收到的數據流進行解碼后,將數據通過背板總線發送到主控模塊,主控模塊把接收到的數據經DS92LV18解串、FIFO緩存,通過USB接口上傳給上位機。

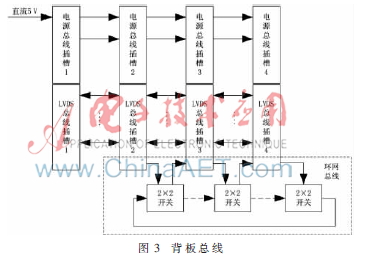

3 背板總線模塊

背板總線模塊是測試儀內部各模塊間的橋梁,包括電源總線和信號總線兩部分。電源模塊通過電源總線為測試儀內部供電;信號總線完成系統內部各模塊之間的通信任務。其中信號總線選用低壓差分信號技術LVDS總線,該總線具有低功耗、低誤碼率、低串擾和低輻射的優點,且可以高達數千Mbps的速度傳送串行數據。

背板總線模塊模塊硬件原理如圖3所示,由4對總線插槽和3個2×2模擬交叉開關組成。4個插槽分別對應電源模塊、主控模塊、綜合數據流測試模塊和數據流模擬源模塊。插槽、槽上的功能模塊以及插槽間的高速2×2模擬交叉開關共同形成自適應的LVDS環網總線,作為測試儀內部信號傳輸總線。

4 綜合數據流測試模塊

綜合數據流測試模塊是實現系統功能的核心單元,主要由阻抗匹配及電平轉換接口、位同步器、碼型變換、幀同步器及參數識別和邏輯控制模塊組成。其原理圖如圖4所示。

本設計中,除輸入端的阻抗匹配及電平轉換接口電路和輸出端的LVDS接口電路,其他功能均通過一片PFGA實現,電路簡潔,方便升級更新。LVDS控制器實現對上位機命令參數的接收、解碼數據的上傳以及位同步和幀同步狀態的上傳。位同步模塊、碼元變換模塊以及幀同步模塊配合實現對不同數據流的解碼,完成通用測試的核心功能。

要實現對不同碼速率的數據流的解碼,就要求系統可以快速準確地生成對應的恢復時鐘,完成位同步。碼同步模塊采用DDS+鑒相器的方案實現同步時鐘的提取[6]。原理框圖如圖5所示。

使用64位的累加器保證DDS分頻精度和分辨率,頻率控制字K由式(1)計算得到。

K=fo×264/fR(1)

其中fR為輸入參考時鐘頻率,fo為待測數據流的碼速率。當接收到參數K時,DDS可快速生成與待測數據流碼速率相同的時鐘。之后還需完成時鐘與信號的對齊,這直接關系到系統的誤碼率及信噪比。當輸入信號出現跳變時,讀取DDS中累加器的sum值、即時相位,可得到時鐘與信號的準確關系,根據超前量或滯后量,對sum進行加K或減K操作,加K即使下一個同步時鐘提前一個參考時鐘周期,減K即使下一個同步時鐘滯后一個參考時鐘周期。同時使用抖動容限值L,當超前或滯后超過L時,直接對同步時鐘進行復位。此種時鐘同步方案完成同步僅需1個時鐘周期,不僅滿足不同碼速率的數據流的測試需求,而且進入同步狀態快速穩定。

待測數據流碼型不盡相同,碼型變換模塊根據碼型參數對其進行運算轉換為NRZ-L碼。完成碼型變換之后,幀同步器將碼型變換后的數據信號流中提取字同步和幀同步信號,產生幀同步和字同步保護信號,從而完成數據分離并獲得正確的數據格式。幀同步信號頻率由位同步信號分頻即可方便得出,然而每幀的開頭和末尾不能由此得到,為實現幀同步,在數字信息流中插入一些特殊碼組作為每幀的頭尾標記,接收端根據這些特殊碼組的位置實現幀同步。

本系統要求通用性,因而幀格式是可編程的,在工作時,上位機通過USB接口進行參數配置,包括幀同步碼組、幀同步誤差容限、幀同步保護系數和幀同步檢碼系數等,下位機將這些參數存入寄存器,串行數據經移位寄存器移位后鎖存,鎖存后的數據與本地同步碼組送入相關檢測器進行檢測。相關檢測器直接關系到幀同步器的速度和精度。一個N位長的數字相關器,U={u1,u2,…,uN}是同步碼組,R={r1,r2,…,rN}是數字相關器任意時刻接收的數據流通過移位寄存器的內容,R與U進行異或運算,得到ri與ui不一致的個數W。W與相關檢測門限ε比較,若W>ε,則認為沒有檢出同步碼,容錯判決輸出;若W≤ε,則同步碼被檢出。

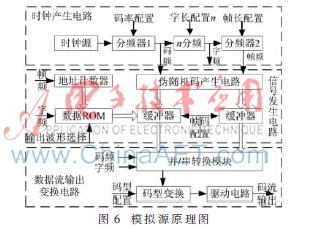

5 模擬源模塊

模擬源產生需要的數據流,實現綜合數據流測試模塊的自檢和其他遙測設備的檢測,由時鐘產生、信號發生和碼型變換3個核心部分組成。時鐘產生根據上位機配置的碼率和幀格式信息產生對應的碼頻、字頻和幀頻信號;信號發生部分在字頻信號控制下從數據ROM中讀出需要的特定波形數據,與同步碼組按指定格式進行編幀;碼型變換部分按照上位機下發的參數將NRZ-L碼變換成NRZ-L/M/S、Bi-φL/M/S。原理圖如圖6所示。

6 結束語

使用LabWindows/CVI編寫了對應的上位機軟件,主界面如圖7所示,通過該軟件對下位機進行參數配置、解碼數據的讀取以及數據的后續處理。模擬源可生成1~10 Mb/s碼速率的PCM數據流,幀格式按IRIG-106標準可編程[7],可輸出正弦波、方波、三角波、鋸齒波、隨機數和固定值6種波形數據,編碼格式NRZ-L/M/S、Bi-φL/M/S 6種可選,單端、差分可選。綜合數據流可實現上述可編程PCM碼流的解調。

參考文獻

[1] 喻金科,徐精華,鄒雄.基于FPGA的可編程PCM解調器的設計[J].微計算機信息,2010,12(2):136-138.

[2] 畢海,李永新,李柯.一種PCM遙測同步解調器的設計[J].電子測量與儀器學報,2000,14(1):66-70.

[3] 甄國涌,林華亮.串行PCM碼流解碼電路設計與應用[J].航空計算技術,2005,35(1):79-81.

[4] 張天平,許斌.基于FPGA的遙測解調系統設計[J].電子元器件應用,2007,9(9):43-46.

[5] 朱旖,杜建軍.國外軍用電子自動測試系統發展綜述[J].電子測量技術,2008,31(8):1-3.

[6] 劉東華,王元欽,袁嗣杰,等.基于瞬時測頻的PCM/FM信號解調方法研究[J].系統仿真學報,2005,17(10):2463-2466.

[7] 李國民,周富大,高維路,等.基于IRIG-106標準的可編程PCM編碼數據采集系統[J].遙測遙控,2003,24(4):27-30.