直接數字合成器,是采用數字技術的一種新型頻率合成技術,他通過控制頻率、相位增量的步長,產生各種不同頻率的信號。他具有一系列的優點;較高的頻率分辨率;可以實現快速的頻率切換;在頻率改變時能夠保持相位的連續;很容易實現頻率、相位和幅度的數控調制等。目前可采用專用芯片或可編程邏輯芯片實現DDS[1],專用的DDS芯片產生的信號波形、功能和控制方式固定,常不能滿足具體需要[2]。可編程邏輯器件具有器件規模大、工作速度快及可編程的硬件特點,并且開發周期短,易于升級,因為非常適合用于實現DDS。

1 DDS的工作原理

DDS的結構原理圖如圖1所示,DDS以數控振蕩器的方式,產生頻率、相位和幅度可控的正弦波[3]。電路包括了相位累加器、相位調制器、正弦ROM查找表、基準時鐘源、D/A轉換器等組成。其中前三者是DDS結構中的數字部分,具有數控頻率合成的功能。

DDS系統的核心是相位累加器,完成相位累加過程。在基準時鐘的控制下,頻率控制字由累加器累加,以得到相應的相位數據,相位調制器接收相位累加器的相位輸出,主要用于信號的相位調制,其輸出的數據作為取樣地址來尋址正弦ROM查找表,完成相位-幅度變換,輸出不同的幅度編碼;再經過D/A轉換器得到相應的階梯波;最后經低通濾波器對階梯進行平滑處理,即可得到由頻率控制字決定的連續變換輸出的正弦波。

2 基于DSP Builder和DDS設計

2.1 DSP Builder簡介

DSP Builder是美國Altera公司推出的一個面向DSP開發的系統級工具,他作為Matlab的一個Simulink工具箱,使得用FPGA設計DSP系統完全通過Simulink的圖形化界面進行建模、系統級仿真,設計模型可直接向VHDL硬件描述語言轉換,并自動調用QuartusⅡ等EDA設計軟件,完成綜合、網表生成以及器件適配乃至FPGA的配置下載,使得系統描述與硬件實現有機的融合為一體,充分體現了現代電子技術自動化開發的特點與優勢。

2.2 DSP Builder設計原理及參數設置

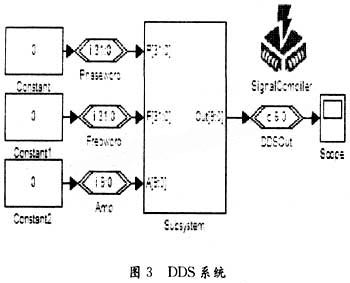

基于DSP Builder的DDS系統如圖2和圖3所示,DDS子系統Subsystem有3個輸入,分別為Freqword(32位頻率控制字)、Phaseword(32位相位控制字)、Amp(10位幅度控制字);一個輸出,即10位DDSOut輸出。2個Parallel Adder Subtractor分別為相位累加器和相位調制器,LUT為正弦ROM查找表。設置Simulink的仿真停止時間stop time為5,仿真步進Fixed Step Size為le-3。圖(4)對應頻率、相位和幅度控制字分別為4000000,0和10(參數1)時DDS系統的輸出波形,圖5對應頻率、相位和幅度控制字分別為9000000,500000000和15(參數2)時DDS系統的輸出波形。

3 基于FPGA的DDS設計

3.1 DDS的FPGA實現

Matlab/Simulink對已經設計好的DDS系統進行編譯,通過調用DSP Builder的SignalCompiler工具可直接生成QuartusⅡ 工程文件,再調用QuartusⅡ完成綜合,網表生成和適配,直至完成FPGA的配置下載過程。

本設計方案采用的FPGA芯片是Altera公司的Cyclone系列芯片EP1C6Q240C8,,其容量6000個邏輯宏單元,等效于標準15萬邏輯門電路,速度為-8,完成可通過單片芯片電路實現DDS,相位累加和相位調制器均為32位,正弦ROM查找表存儲1024×10b波形數據,系統時鐘為55.6MHz,利用FPGA可以根據需要方便地實現各種比較復雜的調頻,調相和調幅功能,具有浪費的實時性。

3.2 仿真結果

使用QuartusⅡ對DSP builder生成的工程文件進行仿真,針對不同參數設置的DDS系統,其仿真波形圖如圖6和圖7所示。

圖中,clock為系統時鐘,sclrp為高電平復位信號,iFreqwords,iPhasewords和iAmps分別為輸入頻率、相位和幅度控制字,oDDSOut為輸出信號。當復位信號sclrp到來后,向相位累加器賦0,并向相位調制器賦一個初始相位值,在時鐘信號的控制下,頻率控制字控制相位累加器累加,相位調制器進行相位調制,其輸出數據作為取樣地址尋址ROM查找表,便可以在oDDSOut管腳上輸出連續的正弦波信號。在不同的參數設置下,QuartusⅡ中的仿真結果與Matlab/Simulink中的仿真結果在相位,頻率和幅度上基本一致。利用FPGA能輸出較高質量的信號,雖然內部數字信號有一定的抖動,但通過采用抖動注入技術、延時疊加法等[3]方法,通常也能將誤差保持在允許范圍之內。

4 結論

利用可編程邏輯芯片設計DDS的方法通常是采用VHDL語言輸入和原理圖法相結合來設計整個信號發生電路,這種方法通常需要調用很多模塊,綜合性較強,對設計者要求較高。本文利用QuartusⅡ和Matlab/Simulink之間的接口工具DSP Builder來設計整個DDS系統,DSP Builder具備一個友好的開發環境,并且和QuartusⅡ交互性強,易于使用。設計者只需簡單了解VHDL描述語言,就可以直接調用已經建立好的Matlab和Simulink設計流程,通過Simulink的圖形化界面進行建模、系統級仿真,并子對調用QuartusⅡ進行綜合,網表生成和適配,最后完成向FPGA的配置下載過程。整個設計思路靈活,圖形界面簡單直觀,開發周期短。仿真結果表明,該設計方案原理正確,行之有效。用FPGA實現DDS較專用DDS芯片更為靈活,只要改變FPGA中ROM內的數據和控制參數,DDS就可以產生任意調制波形,且分辨率高,具有相當大的靈活性。將DDS設計嵌入到FPGA芯片所構成的系統中,其系統成本并不會增加多少,而購買專用芯片的價格則是前者的很多倍。所以采用FPGA設計DDS系統具有很高的性價比。