摘 要:針對路由器高可用性" title="高可用性">高可用性系統中心跳探測模塊的常見問題,提出一套新型基于網絡層" title="網絡層">網絡層自動調頻的心跳探測方案。該方案采用雙心跳線,結合動態調節探測周期的方法,并在網絡層中實現。

關鍵詞:高可用性? 心跳? 網絡層

?

??? 計算機網絡已經成為現代社會生產和生活的基礎設施,而核心路由器作為網絡的關鍵結點,能否保證服務的可靠性和穩定性是一個極為重要的問題。核心路由器一般承擔著骨干網的運營,如果發生致命故障,將導致大面積網絡的癱瘓,造成的直接經濟損失也是巨大的。

一般的解決方法是采用雙機熱備的主從切換方式,如CISCO的HRSP協議所介紹的一種方法,由一臺active路由器和standby路由器組來承擔高可靠性。而本文討論的是核心路由器如何解決主備主控板的切換來保證高可靠性的問題。這樣就產生了一個問題,即如何設計一種及時且準確的探測機制來發現主控板故障,這是能否實現主備切換的基礎。

? ? 本文就已有的心跳(Heartbeat)探測機制存在的優點和不足進行討論,并設計了一種基于網絡層的可自動調頻心跳保障模型。

1 Heartbeat介紹

Heartbeat網絡是故障發生時系統間的通信通道。簡單地說,系統通過心跳網絡進行周期性的問候信息交流。系統在正常情況下,備用處理器發送信息詢問主用處理器的健康狀況,主用處理器同樣發送心跳探測包來確定備用處理器是否隨時處于等待狀態。如果備用處理器在限定的周期內未收到主用處理器的探測包,則表明主用處理器發生故障,它會自動接管主用處理器的IP地址和各種應用服務,成為新的主用處理器。當失效處理器恢復正常后,重新發狀態信息給新的主用處理器,要求其成為備用處理器。

現有的心跳網絡連接方式多借助于RS232串行線路和以太網方式。由于心跳網絡相對于整個網絡所傳輸的數據量要小,但對其可靠性要求很高,即零丟包率,否則連續的數據丟失會引起對方處理器誤認為其宕機。因以太網價格低廉、應用廣泛、不需要特殊的電纜和硬件設備,所以通常被推薦用來實現心跳網絡。此外其他網絡介質也沒有其傳輸可靠性高。對于傳輸大量數據流的情況,推薦使用快速傳輸網絡,但是心跳數據信息相對較小,現有Heartbeat探測主要存在以下問題。

(1) 硬件問題造成的誤判

??? 主從雙處理器的設計目的是為了避免SPOF(單點故障)造成停機。而心跳線同樣可以成為SPOF。當處理器收不到對方的心跳信息時,故障原因分為兩種,一種是主處理器軟硬件的故障;另一種可能是心跳線路自身的故障。對于前一種情況確實應該觸發主備切換措施,而第二種情況可能會造成系統誤判而進行主備切換,主備處理器切換必然要造成路由器短時間的異常工作,所以確定故障的原因比較困難。

? (2) 心跳周期難以設定

????作為判斷故障的心跳模塊自身必須可靠穩定,所以一般設計比較簡單。而心跳周期長度一般采用人為設置,但是這個周期是否合理?即是否可以及時發現故障,且其發送探測的頻率過高又不會造成多余的系統負擔。以上兩個相互制約的因素都是高可用性要考慮的問題。

??? 在實際應用中,心跳網絡一般處于變化的請求服務中,如果系統采用固定心跳周期,有可能弱化系統的可用性;如果周期過短,處理器需要頻繁處理心跳探測數據,影響了系統的效率;如果周期過長,在故障發生時,從處理器可能沒有及時發現探測心跳未到達而延誤觸發主備切換模塊,造成的網絡癱瘓更與高可用性的要求背道而馳。

?? (3) 心跳鏈路" title="鏈路">鏈路采用套接字以TCP/UDP方式的傳輸機制造成較大的時延

??? 作為對實時性" title="實時性">實時性和可靠性有雙重要求的心跳鏈路,多數方案都在應用層" title="應用層">應用層利用SOCKET以UDP或TCP報文方式實現心跳協議。其中UDP報文比TCP報文簡短,正好符合心跳協議的要求。由于UDP沒有擁塞控制,所以心跳網絡如果出現擁塞,UDP會丟棄一些數據包,但不會影響處理器發送心跳的速率,同時也帶來不可靠傳輸的問題。如果網絡在擁塞情況下會丟失一些數據包,這對于零丟包率的心跳檢測將造成很大影響。

在傳輸速率問題上,無論對于TCP還是UDP的套接字,實現方式都在應用層實現,即心跳報文要經過傳輸層、內核及接口,并受到應用層任務切換的影響,這樣會導致切換時間長達數秒,難以滿足實時性的要求。

在可靠性問題上,如果是單對心跳網絡,則可以對探測包進行編號,并利用判別機制裁決。忽略收到非連續編號的數據包的情況,判斷因為心跳網絡擁塞所致,而不影響心跳信任級別的周期。但如果采用雙心跳線網絡,在兩條鏈路上同時出現擁塞情況的可能性較小,因而避免了由于不可靠傳輸造成的誤判。

2 自動調頻雙心跳保障模型設計方案

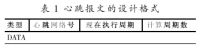

????根據上述在心跳探測技術中出現的問題,筆者提出一種基于網絡層的自動調頻雙心跳保障方案。此方案流程如圖1,圖中的報文類型見表1。

?

?

?

????在路由器啟動后,兩塊處理器均屬于初始狀態,這時尚未確定active和standby。首先僅在一條心跳線上啟動主備協商機制。要求主備協商機制要簡約,因為在這里沒有必要設計復雜的算法選出主用。因而采取比較兩處理板IP地址大小的判決方法,通過互發心跳探測報文,比較IP ADDR值,較小的為主處理器,進入active狀態;較大的為備用處理器,進入standby狀態。

????在確定了主備用地位的同時,向對方通告自己的身份。這時啟動雙心跳線,備用一方發送心跳探測報文監控主用的工作是否正常;主用收到探測報文進行回復。備用在工作時要根據主用發送回復的周期值,計算出系統最合適的心跳探測頻率,后文將詳細介紹。為了避免由于心跳線發生故障造成的誤判,如果備用只收到來自一條心跳線的回復報文,則由故障判別機制來確認主用工作正常。

??? 報文類型:00為主備協商報文,DATA域攜帶處理器IP地址;01為主備確定報文,DATA域攜帶裁決結果;10為心跳探測報文,standby→active,要求active給確認;11為心跳回應報文,active→standby,告訴standby自己正常。

2.1 雙心跳網絡探測機制及故障辨別機制

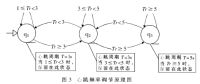

分別由兩個進程各自控制兩條心跳線路上的心跳數據發送,由故障判別機制判斷處理器的工作狀態。例如,若從處理器收到來自兩條鏈路的心跳信息,則判斷主處理器為正常工作狀態;若從處理器只收到一條鏈路上的心跳信息,則判斷主處理器工作正常,且心跳線故障,不觸發主備切換模塊;若從處理器未收到任意一條線路的心跳信息,則判斷主處理器失效,觸發主備切換模塊。此設計雖然增加了實現的復雜性,但卻解決了實際工程中接口松動等問題造成的系統誤判和不必要的消耗。雙心跳網絡探測機制如圖2所示。

?

??? 在功能實現上,故障判別機制和傳統定時器的作用是相同的。對于傳統定時器方式:在處理器未收到對方的心跳信息時,啟動定時器,在所設置的時間內仍沒有收到信息,判斷為處理器失效,這時由于等待deadline可能已經延誤了主備切換的時間。

??? 由于本方案采取冗余心跳網絡,對于一條心跳鏈路來說,如果處理器未收到心跳信息,則進入故障判別模式,詢問另一條心跳線是否收到心跳信息;如果結果一致,則迅速啟動主備切換。這樣可以減少不必要的等待時間,也可以避免由于線路擁塞造成的誤判。

2.2 分級的自適應周期設計

??? 針對心跳周期難以設定的問題,采用了一種自適應周期的設計。其原理是:首先設定高、中、低三種心跳信任級別的周期:1s、3s、5s。心跳頻率調節原理如圖3所示,通過最近發生的N次心跳求其平均值Tr與三個級別相比較,以確定其下一階段采用的心跳頻率。這樣可以根據實際網絡運行的情況實現高可用性。

?

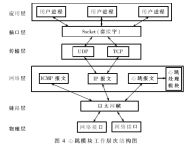

2.3 基于網絡層的心跳傳輸機制設計

??? 由于以往的心跳傳輸基本采用TCP或UDP方式,在實現中必須遵從TCP/IP協議信息處理的層次流程,使實時性的要求無法保證。為了縮短處理時經過的層次,設計了一種基于網絡層的心跳傳輸方式。

心跳模塊工作層次結構圖如圖4所示。心跳模塊與上層應用完全分隔開,它處于鏈路層和網絡層。通過在鏈路層對幀頭的類型字段的檢查,區分出心跳報文與IP報文。如果是IP報文,則送入上層協議棧;如果是心跳報文,則進入心跳報文隊列,并觸發一個中斷,通告心跳模塊進行處理。以往通過應用層的心跳信息必須通過插口層再到應用層進行處理,這個過程要經過路由、選徑、報文確認等一對一地心跳傳輸中所不必要的步驟,增加了網絡的開銷,更降低了傳輸效率。

?

?

以上設計的方案在ACR路由器的主控支撐軟件主備切換模塊中,已成為心跳探測機制工作中關鍵的一環。實踐證明,此方案不僅在發現故障上實現了最低延遲,同時將誤判率降至最低,為主備切換做好了基礎性工作。從而為保證系統可靠性提供了前提。但在實現時增加了系統的復雜性,因此如何設計一個高效、準確且實用的心跳協議仍是雙機熱備系統設計中需認真考慮的關鍵問題之一。

參考文獻

[1]?尹康凱,王明偉,李善平.高可用性機群中多個節點的心跳模型研究.計算機工程,2005.

[2]?David Patterson,Aaron Brown, Pete Broadwell. Recovery??oriented computing(ROC): motivation,definition,techniques,and case STUDIES[R].Technical Report CSD-02-1175,UC Berkeley,2002.

[3]?Sameer Srivastava. Redundancy management for network?devices. 2003. IEEE

[4]?Evan Marcus,Hal Stern. 高可用性系統設計.北京:清華大學出版社,2005.

[5]?John L H, David A P. Computer architecture: A quantitative approach[M].北京:機械工業出版社,?2002.