雷達從體制上可以分為相參雷達和非相參雷達,由于磁控管發射機的起始相位不固定、存在幅度抖動和頻率漂移,對接收回波無法做相參積累,所以采用磁控管發射機的雷達屬于非相參雷達。而現代信號處理中相參積累可以獲得更大的增益和更多的功能,例如成像或動目標檢測都需要發射和接收信號具有相參性。因此對原有非相參雷達進行相參改進成為提高雷達性能的關鍵。

非相參雷達相參化主要是在信號處理部分來實現,這樣既可以節約成本又便于改造實現。而信號處理的核心就是數字穩定校正(DSU),DSU的主要作用就是消除發射信號的相位抖動,使接收信號具有相參性。

在數字技術飛速發展的今天,信號處理的硬件實現主要有FPGA和DSP等來實現。大規模可編程邏輯器件FPGA在處理速度和集成度等方面發展很快,用戶可自定義邏輯功能、可重復編程,同時FPGA還具有成本低、使用靈活方便等優點,在雷達信號處理硬件實現中得到廣泛的應用。由于雷達信號處理數據量大、實時性強、動態范圍大和數據精度高,結合片內存儲能力本文選用ALTERA公司的StratixⅡ系列芯片。

1 數字穩定校正單元的工作原理

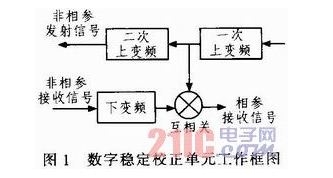

數字穩定校正單元(DSU)的主要作用是實現接收信號的相參處理,DSU是利用發射信號對接收的回波信號進行匹配來獲得相參性。DSU工作的原理框圖如圖1所示。

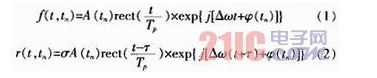

假設這里只考慮脈沖間的幅相不一致,可得發射信號和接收信號的基帶形式可以表示為

式中:t為快時間表示,tn表示第n個發射或接收脈沖;A(tn)為第n個發射脈沖隨機振幅;φ(tn)為第n個發射脈沖隨機相位函數;σ為包含傳播衰減和目標散射的系數;rect(t/Tp)為發射脈沖矩形包絡函數;Tp為脈沖寬度;△ω為雷達發射機自頻調系統靜差;τ為接收目標回波的延時。

可見DSU利用A/D對發射脈沖樣本進行取樣,然后用該取樣值和回波信號進行相關或卷積來實現相位校正,達到消除隨機初相的目的。經后續能量歸一可以消除幅度不穩定造成的影響。所以經過DSU處理,可以消除或減小磁控管產生的發射脈沖幅相不穩定性。

2 基于FPGA的DSU實現

由于本雷達信號處理數據量大、實時性強、動態范圍大和數據精度高,結合片內乘法器和存儲能力本文選一片ALTERA公司的StratixⅡ系列EP2S90 FPGA芯片。StratixⅡ系列的EP2S90器件具有152個接收機和156個發送機通道、支持1Gbps的高速差分I/O信號、具有LVDS、LVPECL和Hyper Transport標準接口、具有9Mbit的RAM存儲器、允許設計者將外掛SRAM和DRAM大容量存儲器件。

整個處理流程如下:發射脈沖信號在進入信號處理模塊后,首先進行A/D采樣,對采樣后的數據進行正交分解形成I、O兩路信號,這里發射脈沖內采樣為16個數據,發射脈沖數據在發射樣本采樣門的控制下分I、Q兩路存儲到發射脈沖存儲區,作為DSU相關的權函數使用,記為fI和fQ;接收回波信號在A/D采樣后,經過正交分解形成數據流rI和rQ,然后對接收數據進行相關操作,即回波數據以流水方式通過相關器與發射樣本數據逐點進行乘加處理。

本論文涉及的內容是從發射脈沖信號和接收數據正交變換后的處理過程,即實現接收數據和發射脈沖樣本進行相關的操作。DSU處理的計算公式如下:

這里采取在FPGA內完成相關運算,而對幅度的歸一化可采用浮點運算能力較強的DSP器件完成。因為在FPGA內實現除法運算一般采用查表法和,查表法缺點是需要預先存儲所有可能值的倒數,然后根據計算出的能量查找相應倒數,取出表中存儲的倒數值再做乘法最終實現除法功能。可見再FPGA中實現除法(尤其是系數不固定)比較復雜。而在DSP內部實現除法運算比在FPGA內部實現要更加簡單,而且DSP運算基于浮點操作,精度更高。而DSP芯片內的除法可以由乘以相應的倒數得到。能量的倒數通過一次求均方根倒數和一次乘法實現,運算量很小。所以能量歸一化運算本文選擇在DSP內部完成,實現更簡單、精度更高。

經過FPGA中的DSU和DSP中的能量歸一,接收信號數據已經消除了發射信號的初相抖動和發射幅度不穩定的影響,形成了相參的信號。基于FPGA的DSU實現框圖如圖2所示,主要包括3個模塊,模塊1完成發射樣本形成濾波器系數和接收數據時序控制;模塊2完成對相關后數據的多路選擇功能,形成相關后數據流;模塊3完成接收數據和發射脈沖樣本進行相關操作,由于每個接收數據要進行16次的乘法運算,所以我們同時形成16個乘加模塊進行運算。

3 接收機仿真結果

本系統仿真設計是在Quartus II 7.2(32-Bit)環境下進行的,編程代碼采用VHDL語言進行編寫,硬件芯片平臺選擇ALTERA公司的Strat ixⅡ系列EP2S90 FPGA芯片。

系統設計端口定義如下:

ad_clk:數據AD采樣時鐘

RST:系統復位信號

ad_din[31..0]:數據輸入端口,發射數據和接收數據復用

acq_en1:對發射數據采集使能信號

acq_en2:對接收數據采集使能信號

fifo_wr_clk:DSU相參處理后輸出數據時鐘

fifo_wr_en:DSU相參處理后輸出數據使能

fifo_data[31..0]:DSU相參處理后輸出數據端口,高16位為I、低16位為Q

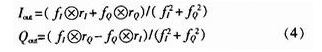

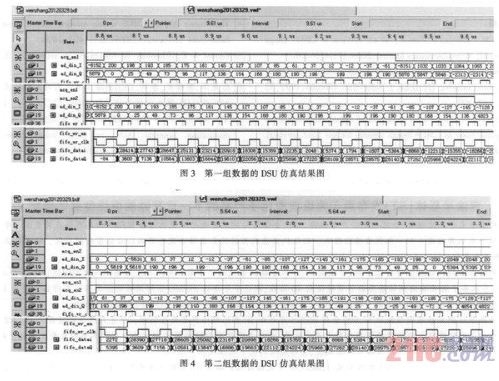

仿真中取兩組發射和接收數據分別進行DSU處理,仿真結果如圖3、4所示,從fifo_datai和fifo_dataiQ(即fifo_data[3操1..0])可以看出,兩組初相不同的數據經過DSU處理后得到了基本一致的結果,即去掉了發射信號的相位抖動。比較圖3和圖4的fifo_datai和fifo_dat aiQ可以發現兩者并不完全一樣,這時由于FPGA編程為定點數作造成的。

4 結論

該方法基于StratixⅡ系列的EP2S90 FPGA芯片實現了數字穩定校正功能,消除了發射信號的相位隨機,使接收信號具有相參性。仿真結果表明了本文所述基于FPGA的DSU實現方法有效,另外該算法已經實際用于某非相參雷達改造上,并進行了外場實驗,取得了良好的實測效果。