關鍵詞:FPGA;動態部分重構;重構;Virtex

隨著可編程技術的不斷發展,FPGA被廣泛應用于電子設計的各個領域。新的設計思想和設計方法也被不斷的提出和應用,如FPGA的動態部分重構技術。所謂 動態重構是指對于時序變化的數字邏輯系統,其時序邏輯的發生,不是通過調用芯片內不同區域不同邏輯資源的組合來實現,而是通過對具有專門緩存邏輯資源的 FPGA,進行局部和全局芯片邏輯的動態重構而快速實現。動態可重構FPGA器件在編程結構上應具有專門的特征,其內部邏輯塊和內連線的改變可以通過讀取 不同的配置比特流文件來實現邏輯重建。動態部分重構是指重新配置FPGA的部分區域,重構過程中,FPGA其余部分的工作狀態不受影響。此方式減小了重構 范圍和單元數目,從而大大縮短了FPGA的重構時間。

應用FPGA動態部分重構功能使硬件設計更加靈活,可用于硬件的遠程升級、系統容錯和演化硬件以及通信平臺設計[1]等。動態部分重構可以通過兩種方法實現:基于模塊化設計方法(Module-Based Partial Reconfiguration)和基于差別的設計方法(Difference-Based Partial Reconfiguration),本文以基于模塊化設計為例說明實現部分重構的方法。

1 FPGA配置原理簡介

本文針對Xilinx公司的FPGA進行研究,支持模塊化動態部分重構的器件族有Virtex/-II/-E和Virtex-II Pro。

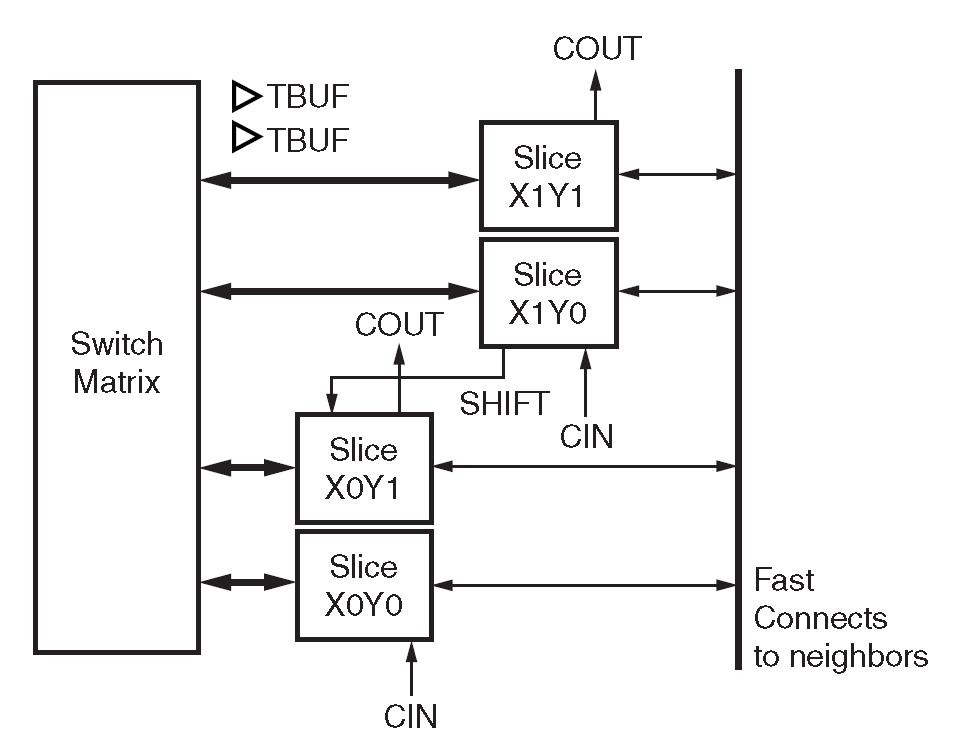

Xilinx公司FPGA是基于SRAM工藝的,包括配置邏輯塊(CLBs),輸入輸出塊(IOBs),塊RAMs,時鐘資源和編程布線等資源[2]。CLBs是構造用戶所需邏輯的功能單元,IOBs提供封裝引腿與內部信號引線的接口。可編程互連資源提供布線通道連接可配置元件的輸入和輸出到相應的網絡。

存儲在內部配置存儲器單元中的數值決定了FPGA實現的邏輯功能和互接方式。Virtex FPGA的配置存儲器是由配置列(Configuration Columns)組成的,這些配置列以垂直陣列的方式排列,如圖1給出了Virtex-E XCV600E器件的配置列構成圖。配置存儲器可分為五種配置列:Center 列包含四個全局時鐘的配置信息;兩個IOB 列存儲位于器件左邊和右邊所有IOBs的配置信息;CLB列存儲FPGA基本邏輯功能的配置信息;Block SelectRAM Content列存儲內部塊RAM的配置信息;Block SelectRAM Interconnect列存儲內部塊RAM間互聯的配置信息[3]。

圖1 Virtex-E XCV600E的配置列構成及地址

配置列根據分配給它的配置地址(Configuration Address)來尋址。每一個配置列在FPGA內都有唯一的主地址(Major Address)空間。

FPGA的邏輯功能通過配置比特流(Configuration Bitstream)來實現。對于動態部分重構功能來說,需重構的配置邏輯是通過下載不同的部分配置比特流來實現的。

2基于模塊化動態部分重構FPGA的設計方法

所謂的FPGA模塊化設計就是將系統按照一定規則劃分成若干模塊,然后對每個模塊分別進行設計、綜合,并將實現結果約束在預先設置好的區域內,最后將所有模塊的實現結果有機的組織起來完成整個系統的設計[4]。其劃分模塊的基本原則為:子模塊功能相對獨立,模塊內部聯系盡量緊密,模塊間的連接盡量簡單。對于那些難以滿足模塊劃分準則的具有強內部關聯的設計,不適合采用此設計方法。

FPGA模塊化設計的優點在于:團隊式并行工作從而加速整個項目的開發進度;每個子模塊都能夠靈活使用綜合和實現工具獨立進行優化,從而達到更好的優化結果;調試、更改某個子模塊時,不會影響其他模塊的實現結果,保證了整個設計的穩定性與可靠性。

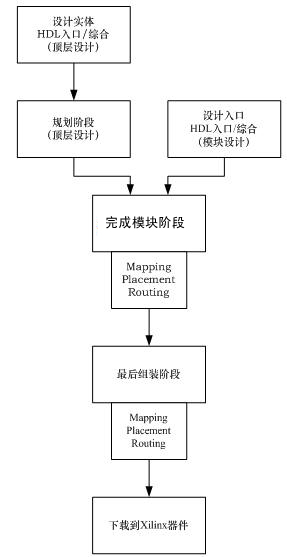

模塊化設計方法使用Xilinx公司的ISE軟件設計工具,常用HDL語言作為設計輸入,頂層模塊描述設計的全局邏輯,包括設計的輸入/輸出、所有子模塊 的黑盒子(Black Box)聲明以及子模塊之間的連接關系。所謂黑盒子聲明是指在頂層模塊中僅僅對子模塊進行端口描述與信號屬性聲明,并不包含任何實際邏輯和時序關系的描 述。子模塊通常也使用HDL語言描述,分別設計出各子模塊的邏輯實體并綜合所設計的子模塊。由于子模塊的輸入/輸出并不是整個設計的外部接口,所以在綜合 過程中應禁止子模塊插入I/O端口,而僅在綜合頂層模塊時才插入I/O端口。最后將所有子模塊的實現結果和頂層的實現結果有機地組織起立,完成整個設計的 實現。圖2是基于模塊化設計方法的流程。

采用模塊化設計方法實現FPGA的動態部分重構,首先進行模塊劃分,將設計的固定邏輯即運行過程中不需要更改的邏輯劃分到固定模塊,將需要更改的部分劃分到可重構模塊中。其次模塊的放置位置和大小也有限制,必須遵循一定的規則[5]: 可重構模塊的高度和器件的高度一致,從圖1中可以直觀地認為模塊必須包含整個配置列;可重構模塊的寬度最小是4個Slice(一個CLB包含兩個完全相同 的Slice),并且必須為4個Slice的倍數;如果可重構模塊位于器件的最左邊或是最右邊的Slice列,則所有位于器件邊緣的IOBs將作為可重構 模塊的資源;為了減少設計的復雜度,可重構模塊的數量應該盡量少等。

圖2 模塊化設計流程

3 FPGA動態部分重構的實現

在本設計實例中,FPGA實現的功能是對外圍接口電路進行邏輯控制以及根據外圍不同設備輸入的數據選擇適當的數據處理算法。據此將設計劃分為固定模塊和可 重構模塊,其中固定模塊內實現對外接口的控制邏輯,可重構模塊內實現數據處理算法。本例中只將FPGA的邏輯功能更換一次,即可重構模塊只部分重構一次, 將其在重構前后的不同邏輯功能分別計作reconfig_a和reconfig_b。系統會根據需要動態部分重構FPGA,為不同的數據源選擇適合的處理 方法。本設計由Virtex-E XCV600E器件來實現。

根據模塊所需資源的大小和模塊劃分原則,在用戶約束文件(UCF)中將每個模塊的位置進行約束,如下所示:

INST "fix" AREA_GROUP = "AG_fix" ;(1)

AREA_GROUP "AG_fix" RANGE = CLB_R1C1:CLB_R48C36 ;(2)

INST "reconfig" AREA_GROUP = "AG_reconfig" ; (3)

AREA_GROUP "AG_reconfig" RANGE = CLB_R1C37:CLB_R48C72 ;(4)

其中(2)、(4)指定了兩個模塊的具體位置。

按照模塊化設計流程,分別對固定模塊fix和可重構模塊reconfig_a和reconfig_b進行設計綜合,再將兩個可重構模塊分別和固定模塊進行組合,完成整體設計。此過程中可重構模塊和FPGA的整個設計分別生成配置比特流。

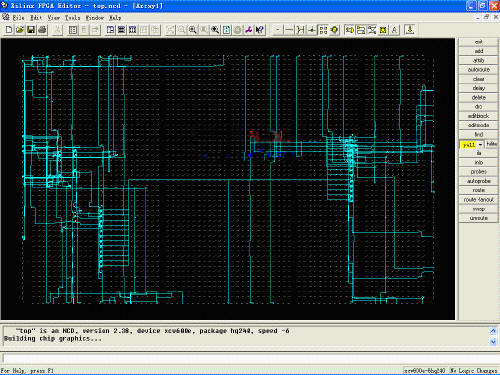

圖3和圖4是FPGA部分重構前后的整個設計的物理實現,圖中左半部分為固定模塊區域,右半部分為可重構模塊區域。從兩圖中可知在部分重構前后可重構模塊區域內布線發生變化,而固定模塊區域內布線沒有發生變化。

圖3 fix和reconfig_a整體設計的物理實現結果

圖4 fix和reconfig_b整體設計的物理實現結果

FPGA動態部分重構時首先須將整個配置文件下載到器件中,重構時系統根據運行的需要選擇適合的部分重構配置比特流。Virtex-E XCV600E配置比特流的大小為495204個字節,而可重構模塊reconfig_a和reconfig_b配置比特流的大小分別為93324個字節 和111868個字節,因此采用部分重構不僅能夠在運行不間斷的情況下更新可重構模塊區域內的邏輯功能,而且也能使重構配置時間大大減少。www.51kaifa.com

3 結論

本文以Xilinx FPGA為研究對象,介紹了采用模塊化設計實現FPGA動態部分重構功能的方法。FPGA的動態部分重構功能使硬件設計更加靈活,可以將不同設計定位到芯 片內同一邏輯資源部分,重構此部分邏輯資源,同時保持其他部分電路功能正常,從而靈活快速的改變系統設計,能夠減少器件的花費,降低功耗、更有效的利用電 路板空間,可以應用于系統實時容錯、自適應硬件算法等。

本文作者創新點:基于FPGA動態可重構技術將設計從一個純空間的數字邏輯系統轉換為在時間、空間混合構建的數字邏輯系統。這種技術是數字系統設計方法、 設計思想的變革,使FPGA資源利用率成倍提高。目前我國在FPGA可重構技術方面開展的研究很少。本論文闡述了采用模塊化設計實現FPGA動態部分重構 的方法,能夠使FPGA部分邏輯功能重新配置過程中,其余部分邏輯功能正常運行,即實現了FPGA邏輯功能的動態部分重構。

參考文獻

[1]張海亮,趙行波,王亮,周祖成. 基于FPGA的可配置通信平臺設計[J].微計算機信息,2006,(32)

[2] Xilinx,Inc.Virtex-E 1.8V Field Programmable Gate Arrays ,http://www.xilinx.com

[3] Xilinx,Inc. XAPP151 “Virtex Series Configuration Architecture User Guide”(2004),

http://www.xilinx.com www.51kaifa.com

[4] Xilinx,Inc.Development System Reference Guide, http://www.xilinx.com

[5]Xilinx,Inc.XAPP290 “Two Flows for Partial Reconfiguration: Module Based or Difference ”,http://www.xilinx.com www