數字信號處理器(DSP)是采用數字計算方法對信號進行處理的專用芯片。由于其性能穩定,可大規模集成,編程性高和易實現等優點,被廣泛應用。其中,以圖像處理與DSP技術結合較為普遍,因為圖像所包含的信息數據量大,而DSP的處理速度快,易于實現大量數據高速傳輸的特點能夠滿足這一要求。

目前,圖像處理技術已在通信、信息、電子、航天及軍事等領域得到廣泛應用。與圖像處理有關的系統設計中,FPGA加DSP構架是普遍的使用方法。為充分利用DSP的性能,需要在FPGA中對圖像進行相應的預處理,再把圖像數據傳輸給DSP進行處理。所以FPGA與DSP之間的數據傳輸技術變得不可或缺。

圖像數據傳輸的速度與穩定性對整個系統的性能具有很大的影響。本文介紹了一種基于EDMA的高速穩定的數據傳輸方法,并在TI的DSP開發平臺CCS下,對該方法的性能進行了測試。

1 方案設計

文中圖像傳輸硬件系統結構如圖1所示。該系統中采用Ahera公司的Cyclone3系列FPGA:EP3C80F484C6,Analog Device公司的視頻解碼芯片ADV7183,差分輸入14位數據的LVDS接口和TI公司的TMS320C6416。該系統既可采集模擬視頻信號,又可采集數字視頻信號。模擬信號經過模數轉換芯片ADV7183后變成數字信號,數字信號經由LVDS差分接口進入FPGA。為調試方便,模擬圖像與數字圖像統一使用320×256規格。DSP以EDMA方式接收,經過FPGA預處理后的圖像數據,在CCS平臺下進行顯示以驗證傳輸的正確性。

2 接口電路設計

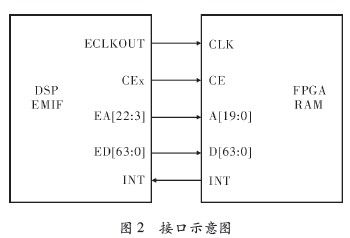

DSP以EDMA方式從FPGA中讀取數據,需要FPGA在內部配置一塊大小適當的存儲空間。FPGA作為一個存儲器,通過DSP的外部存儲器接口(EMIF)與DSP相連。硬件連接如圖2所示。

圖2所示為FPGA與DSP的硬件上連接示意圖。實際使用時,并沒有使用上述所有信號線。FPGA使用到的管腳如下:CLK,CE,A[19:0],D[63:0]和INT。CLK是DSP提供的同步讀寫時鐘,CE是DSP的片選信號,A[19:0]為地址線,D[63:0]地址線。INT為中斷信號。

FPGA與DSP的傳輸機制:FPGA使用QuartusII開發平臺往雙口RAM中寫數,寫滿后用中斷管腳INT來通知DSP讀數。DSP收到FPGA的中斷信號后,開始讀數。讀數期間片選信號CE有效,FPGA把DSP片選信號CE作為雙口RAM的讀使能,在使能期間用DSP提供的時鐘CLK讀取數據。

系統中DSP提供給FPGA的時鐘CLK為100MHz。接收模擬圖像時,圖像數據為8位,只使用D[7:0]8根數據線;接收數字圖像時,圖像數據為14位,使用D[15:0]16根數據線,高兩位置0。數字圖像與模擬圖像均為320×256。

3 EDMA傳輸

TMS320C6000系列DSP中的,增強型直接存儲器訪問(EDMA)控制器執行所有二級高速緩存/內存控制器與外設之間的數據傳輸。

EDMA控制器包括事件和中斷處理寄存器、事件編碼器、參數RAM和地址產生硬件電路。事件是觸發EDMA啟動的同步信號,事件寄存器用于捕獲EDMA事件。事件編碼器解決多個事件發生時事件的優先級問題。對應事件的傳輸參數存儲在EDMA參數RAM中,并且傳遞給地址產生硬件單元,進行尋址EMIF或外設執行相應的讀寫操作。

3.1 傳輸流程

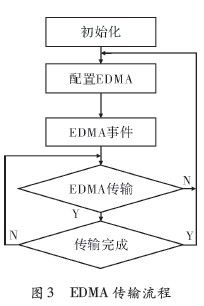

使用EDMA數據傳輸的方法有兩種,一種是CPU初始化的EDMA;第二種是事件觸發的EDMA。所有的EDMA通道都有一個特定的同步事件與之對應,如外圍設備事件、外部硬件中斷或EDMA傳輸完成事件都可以同步觸發EDMA的傳輸。當通道對應的同步事件發生或由CPU同步該通道時,通道就完成一次數據傳輸請求。由事件觸發的EDMA傳輸實時性好,是一種常見的傳輸方式。系統采用的就是事件觸發模式,觸發信號就是FP GA給DSP的中斷信號。圖3為EDMA的傳輸流程。

3.2 EDMA配置

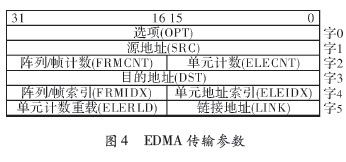

同步事件發生時,EDMA傳輸的數據大小和源目的地址由參數RAM中的參數決定。訪問EDMA的參數RAM時需要通過外圍總線。EDMA傳輸參數,如圖4所示。

選項(OPT)部分主要用于傳輸數據的最小單元、數據傳輸的源地址和目的地址的尋址模式。系統中的最小傳輸單元為1 Byte,源地址設置為一維源,目的地址設置為二維源。數據傳輸模式為幀同步。傳輸數據塊的行數設置255(實際傳輸行數為256),列數設置為320。

源地址(SRC)設置了源數據所在的地址,系統該參數配置為0xA0000000,指向FPGA目的地址(DST)設置了數據要被傳輸到的存儲空間的地址。

實現傳輸過程為把一幅320×256 Byte的圖像從FPGA緩存到了SDRAM中。傳輸14位的數字圖像時,一個像素的圖像數據占用2 Byte,所以要把選項(OPT)中的最小傳輸單元改為2 Byte。

3.3 程序實現

相應的EDMA通道初始化完成后,使能并打開相應的中斷。FPGA每產生一次EDMA同步事件,即往INT管腳發一次中斷信號,EDMA就能完成一次指定要求的傳輸,然后等待下一次同步事件。

4 實驗結果

DSP提供給FPGA的時鐘為100 MHz,傳輸一幅320×256的圖像需要約為0.8 ms。傳輸速度較快,可以滿足圖像快速傳輸以及實時處理的要求。TI的開發平臺CCS可以觀察存儲器中的數據,并把收到的存在存儲器中的數據顯示成圖像,從而可以驗證傳輸的正確性以及穩定性。數據源為模擬圖像時,相機拍攝的原始圖像和DSP收到的圖像如圖5和圖6所示。

數據源為數字信號時,原始圖像為14位數據,TI的仿真平臺只能顯示8位圖像,所以DSP中收到的圖像數據只能以高8位進行顯示,但會丟掉圖像的一些細節,圖像整體偏暗。由于系統采用的數字圖像由中波紅外熱像儀采集,由于視場差別,原始圖像無法采集。圖7為提取高8位圖像數據顯示的圖像。

圖5~圖7中的圖像經過多次傳輸驗證,沒有出現錯誤的圖像。說明該系統實現的圖像數據傳輸滿足圖像實時處理的速度要求以及可靠性要求。

5 結束語

介紹了一種FPGA向DSP的數據傳輸方法,描述了EDMA的特點以及由其控制的數據傳輸的實現過程。所介紹的方法在開發的實驗平臺上,進行了驗證。文中介紹了FPGA向DSP的傳輸,更改EDMA的源地址與目的地址及相關參數可以實現DSP向FPGA的數據傳輸。