摘要:采用Altera公司的Cyclone系列EPlC3T144C8作為控制芯片,QuartusⅡ為軟件平臺,用硬件描速語言設計了一個具有變頻采樣時鐘和16路采樣通道,基于VGA顯示的邏輯分析僅.該設計方案利用FPGA內部的M4K決作為移位寄存器不斷地進行讀進數據的方式,提高了工作速度、性能穩定性以及分析的范圍和質量。該邏輯分析儀實現簡單,價格低,具有較高的使用價值。

關鍵詞:邏輯分析僅;FPGA;采樣;移位寄存器

邏輯分析儀主要采用高速采樣、靈活觸發和大容量存儲等技術來實現對被測數據的捕獲、存儲和定位分析。傳統數據存儲電路將采樣回來的數據先經過鎖存器鎖存,一旦觸發標志有效,再根據采樣時鐘的頻率把鎖存器數據輸出到外接的SRAM。其缺點是速度慢、存儲占用空間大,不適用于大量數據緩存的需求。本文以三星的SDR SDRAM(K4S64632)作為存儲器,通過FPGA內部的M4K塊作為移位寄存器不斷的進行讀進數據的方式,在不中斷程序運行的情況下實現有效數據不間斷的讀進,設置3種采樣模式,結果表明該設計提高了數據的分析范圍和質量。

1 邏輯分析儀總體方案

邏輯分析儀包括:數據采樣、數據存儲、顯示控制3大部分。由于Cyclone芯片EP1C3T144C8理想情況下最大頻率可達到275 MHz,在實際設計中考慮到其誤差,該設計的信號捕獲精度定位在100 MHz。最多16路信號捕獲輸入通道,1路信號觸發通道,可調的采樣時鐘/周期,3種信號采樣模式,使用計算機的的顯示器作為波形顯示屏幕。

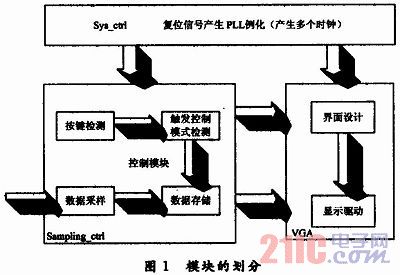

模塊整體上是根據數據流的方向劃分的,如圖1所示。sys_ctrl模塊對系統復位信號進行異步復位、同步釋放,并且通過Cyclone芯片EP1C3T 144C8內部的PLL例化得到多個穩定可靠的時鐘信號。Sampling_ctrl模塊包含按鍵檢測、觸發控制、數據采樣、數據存儲等多個功能是采集控制的核心模塊。VGA顯示模塊包含界面設計、字模數據尋址送顯方式和顯示驅動的時序控制。

2 復位信號產生PPL例化

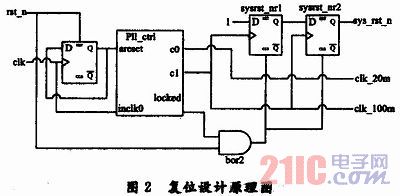

邏輯分析儀的復位設計如圖2所示,這個模塊設計里,先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rat_n異步復位、同步釋放處理,然后將復位信號輸入PLL,同時clk也輸入PLL。在PLL輸出時鐘有效前,系統的其他部分都保持復位狀態。PLL的輸出locked信號在PLL有效輸出之前一直是低電平,等PLL輸出穩定有效之后拉高該信號。FPGA外部輸入復位信號rst_n和locked信號相與作為整個系統的復位信號。從PPL輸出端得到時鐘不僅頻率和相位上比較穩定,而且網絡延時也相比內部的邏輯產生的分配時鐘要小得多。

3 控制模塊

通過FPGA內部的M4K塊配置移位寄存器不斷地讀進新的采樣值,數據采樣回來后先經過SDRAM放入緩存FIFO中,然后把該FIFO中的數據上傳到顯示器。該模塊的時鐘是由PLL電路對FPGA輸入的25 MHz晶振時鐘倍頻得到的。通過FPGA外部一組撥碼開關控制輸入電平為高或者低,從而設置不同的觸發和采樣模式。

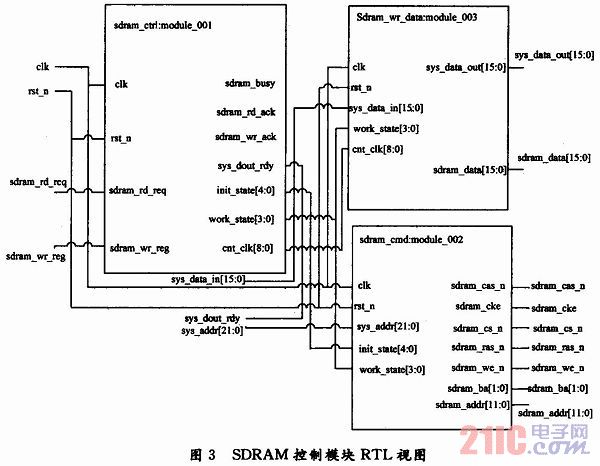

3.1 SDRAM數據存儲模塊

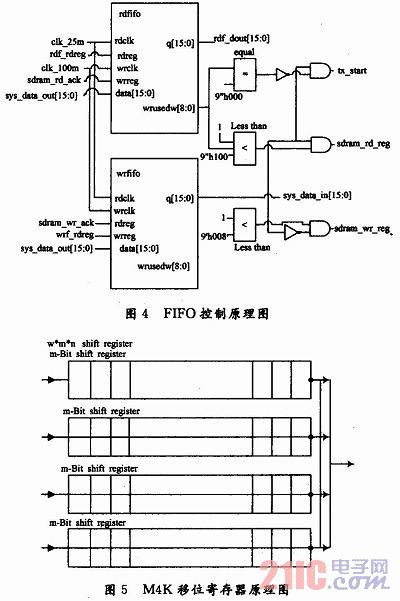

將這個存儲模塊劃分為多個子模塊來實現。如圖3所示。sdram_ctrl是SDRAM狀態控制模塊,該模塊主要完成SDRAM的上電初始化以及定時刷新、讀/寫控制等狀態的變遷。內部設計了兩個狀態機,一個用于上電初始化的狀態控制,另一個月用于正常工作時的狀態控制;sdram _cmd是SDRAM命令模塊,該模塊根據sdram_ctrl模塊的不同狀態指示輸出相應的SDRAM控制命令和地址,sdram_wr_data是SDRAM數據讀/寫模塊,該模塊同樣是根據sdram_ctrl模塊的狀態指示完成SDRAM數據總線的控制,SDRAM的數據讀/寫都在該模塊完成。數據讀/寫借助了兩個存儲器(異步FIFO)如圖4所示。其中wrfifo用于寫SDRAM數據,rdfifo用于讀SDRAM數據。在設計中SDRAM讀/寫都是以8個字(16 b)為單位,使用FIFO中的當前數據量作為操作SDRAM的狀態指示。當wrfifo數量超過8個則發出寫SD]RAM請求,讀出wrfifo中的數據。同樣,在rdfifo數據少于256 B(rd-fifo半空)時發出讀SDRAM請求,讀出8個新的數據寫入rdfifo中,以保證后續電路總是持續的傳輸。SDRAM信號采集模塊在上電延時后從SDRAM的0地址開始寫入遞增數據,隨后通過內部FIFO依次送入SDRAM。SDRAM的所有地址寫完數據后,啟動SDRAM讀邏輯,從0地址開始讀出SDRAM內的數據放入緩存FIFO中,然后把該FIFO中的數據上傳到顯示器。

3.2 基于M4K的移位寄存器連續且可變頻的采樣模塊

為了實現有效效據的精確捕獲在不中斷程序運行的情況下,有效數據長時間實時讀進,提高嵌入式軟件性能分析的范圍和質量。利用Cyclone芯片內部M4K結構配置移位寄存器對數據實時采樣,并且設置2個按鍵調節控制采樣頻率。

圖5為M4K移位寄存器原理圖。配置輸入/輸出的數據位寬w,移位寄存器的一個taps位寬m,總的taps數量n。這三個參數乘積就是占用的M4K存儲大小。從圖5中可看出,每個clk輸入一個移位數據,同時輸出一個數據,而M4K內部則是每個clk周期移位一次,每個tap的輸出直接移位到下一個tap的輸入,配置后的輸出中可看到每個tap的最后一個w位寬的數據。

4 VGA顯示界面的設計

VGA界面設計主要完成對結果的顯示。可以對測試對象的數目、采樣模式、觸發信號的模式、采樣頻率進行控制,并且將結果顯示成為波形圖以便使用者進行觀察。在設計中需要的字符是通過取模軟件PCtoLCD2002,把定義的字模數據存儲在FPGA的M4K塊生成的ROM里,顯示的時候從ROM讀數據進行顯示。

5 FPGA仿真及調試

實時數據采集分析數據量大,時序復雜,以10 kHz~100 MHz的采樣頻率進行數據傳輸時,使用QuartusⅡ自帶的仿真工具生成的激勵,花費的時間長,而且與實際處理結果有一定的偏差,無法有效的驗證整體模塊的功能,同時也贍以對其進行實時模擬。本文在使用QuartusⅡ自帶仿真工具的基礎上,將綜合后得到的結果導入Modesim 6.0中,編寫Testbench提供仿真激勵對邏輯分析儀的頂層模塊進行仿真。通過比較整體功能進行驗證。圖6為邏輯分析儀頂層模塊仿真波形。

由圖6看出,3種采樣模式分別為001,010,100。001采樣模式被觸發后顯示后64個采樣數據;010采樣模式觸發后顯示前32個采樣數據和后32個采樣數據;100采樣模式觸發后顯示前64個采樣數據。清除采樣信號低有效,開始一個新的采樣觸發。經過調試,該邏輯分析儀采樣頻率為100 MHz。在輸入采樣信號的情況下,能夠得到比較不錯的波形。圖7是在該采樣頻率下觀察到的波形。

6 結語

結果表明,該邏輯分析儀以每8個像素為單元作為一個采樣數據的顯示長度,最多16路信號捕獲輸入通道,1路信號觸發通道,3種信號采樣模式,數據的分析范圍和質量得到提高,可方便科研、教學使用。