引言

浮點運算" title="浮點運算">浮點運算作為數字信號處理中最常見的運算之一,各大EDA軟件都帶有免費的浮點運算IP核。通過對IP核的生成和例化來實現浮點運算,把FPGA" title="FPGA">FPGA設計者從繁重的代碼編寫中解脫了出來,同時可以對IP核進行功能剪裁以避免對FPGA邏輯資源的浪費,實現最優設計。但對浮點數的獲取卻關注很少。在浮點運算中,單精度" title="單精度">單精度浮點以其極強的通用性得到了最廣泛的應用。本文將目光集中在單精度浮點數的獲取上,為浮點IP核提供數據源。在數據的傳輸上,ASCII碼是經常采用的一種形式,本文以串口接收到的ASCII碼所表示的實數為例,采用流水處理方式高速地將實數轉換為單精度浮點數。

1 實數轉換為單精度浮點數的原理

1.1 單精度浮點數格式

浮點數的表示遵循IEEE 754標準,它由3部分組成:符號位(sign)、階碼(exponent)和尾數(fraction)。IEEE 754標準規定的單精度浮點數格式占用32位,包含:1位符號位s、8位帶偏移量的指數e[30:23]和23位尾數f[22:0],如圖1。單精度的指數使用正偏值形式表示,指數值的大小從1~254(0和255是特殊值)。采用該種形式表示是為了有利于比較大小,浮點小數在計算時,指數值減去偏正值即是實際的指數大小。其中偏移值(bias)為127,尾數有1位隱藏位。

單精度浮點數包含以下幾種情況:

(1)規格化數:0

(2)(+0,-0):如果e=0且f=0,則V=(-1)s×0;

(3)非規格化數:e=0但f≠0則V為非規格化數;

(4)(+∞,-∞):e=255,且f=0,則V=(-1)s×∞;

(5)NaN(不是一個數):e=255,且f≠0,則V=NaN。

1.2 轉換原理

例如有一個實數為6.91,首先將其轉換為二進制形式表示:110.1110100011110101110000101000。再將其規范化為如下:

6.91=1.101110100011110101110000101000×22則可以得到基本原型:

s:0;

e:2+127(十進制)=129(十進制)=10000001(二進制);

f:101110100011110101110000101000(注:小數部分取28位,且小數點前面的1不要)。

小數部分取28位的目的在于更為準確地表示實數,后五位用于舍入處理。在IEEE 754標準中,舍入處理提供了4種可選方法:就近舍入、朝0舍入、朝+∞舍入和朝-∞舍入,本文采用就近舍入原則。就近舍入的實質就是通常所說的“四舍五入”。例如:尾數超過規定的23位的多余數字是10010,多余位的值超過規定的最低有效值的一半。故最低有效位應增1,若多余的5位是01111則簡單地截尾即可,對多余的5位100 00這種特殊情況:若最低有效位現為0,則截尾;若最低有效位現1,則向上進一位使其變為0。所以,此例中要將最后5位作舍棄處理。得到的結果為:0 100000011011101000111101011100001。組合后等于0100 0000 1101 1101 0001 1110 1011 1000等于40DDIEB8。至此在原理上完成一個實數到單精度浮點數的轉換。

2 在FPGA中實現實數到單精度浮點數轉換的流程

2.1 轉換流程

在實際工程應用中,所處理的數據都有一個或大或小的范圍,在這個范圍內將實數轉換為單精度浮點數會節約芯片資源和降低功耗。故選擇在-9 999.999 9~9 999.999 9的范圍內完成實數到單精度浮點數的轉換,如圖2所示。考慮到實際,數值在很多情況下是通過串口獲取的,并表現為ASCII形式。故本文中所提到的實數皆為ASCII表示。

轉換過程采用流水線操作,用計數器控制轉換進程。ASCII碼轉換為單精度浮點的方法如下:

(1)將8位ASCII碼所代表的數字字符轉為十進制數字(由于硬件電路對數字的表示只有0和1的組合,所以將實數的整數和小數分開表示);

(2)利用程序包里的數據類型轉換函數將十進制數轉換為二進制數,但小數部分的轉換需要單獨實現;

(3)對二進制表示的實數進行規格化;

(4)根據符號位ASCII碼值確定符號位s,根據規格化移動的位數確定階碼e,將規格化中的小數部分f保留28位;

(5)根據就近舍入原則對保留的28位小數部分的后5位進行判斷和舍入。2.2 關鍵代碼解析

在FPGA的硬件描述語言中將整數的十進制轉換為二進制比較簡單,可以調用ISE軟件自帶的程序包中的轉換函數來實現,但如何將小數部分轉換為二進制是能否順利完成從實數到單精度浮點數轉換的關鍵。考慮到要對小數部分進行舍入運算,所以將小數部分轉換28位的二進制。要用28位二進制表示小數部分,需利用VHDL語言中變量(variable)被賦值時立即生效的特性,結合FOR循環來實現。部分關鍵代碼如下:

代碼中frac_part是小數部分的十進制表示(因為integer類型只能表示整數,所以將小數部分擴大了10 000倍,但不影響結果的正確性),frac_28是小數部分的二進制表示。信號frac_28(27)的權值是2-1,依次以1/2倍率遞減,frac_28(0)的權值是2-28。此進程由frac_part發生變化來啟動,完成轉換的時間是瞬時,也可以認為是一個時鐘周期。

3 仿真結果及分析

首先用ModelSim進行功能仿真,其結果如圖3所示。輸入的實數為125.763,輸出結果經Matlab逆向求值同輸入值進行比較,驗證了轉換結果的正確性。一個數的正確轉換并不能說明問題,下面將驗證此轉換方法的可行性。

選取具有代表性的實數對轉換方法的性能進行驗證。主要驗證兩個方面:

(1)是否在預定域內具有全覆蓋性;

(2)是否能對此域中的最小值進行有效表示。

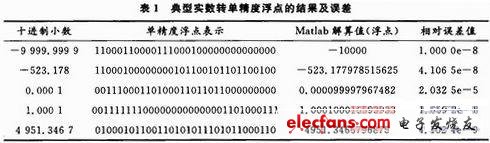

結果如表1所示。

根據轉換原理,最小值所轉換的誤差最大,但最大值的轉換誤差不一定最小(因為存在舍入)。這個最大的轉換誤差在10-5量級,當待轉換實數的絕對值大于整數1時,轉換的誤差將小于10-5量級,可達10-9量級。這樣的轉換誤差可以滿足大多數浮點運算環境下的精度需要。實驗驗證了此轉換方法的有效性和“全覆蓋性”。

在完成仿真測試后,將程序進行綜合,布局布線,最后生成位流文件下載到FPGA芯片中進行驗證。在實際的芯片中將轉換結果和已仿真得到的結果進行比較,并輸出指示信號。從實際的電路輸出結果看,和仿真結果完全一致,證明了此方法在實際芯片中可行性。因為采用的是流水線操作,所以仿真所用的周期數和實際周期數是一致的。該實驗在50 MHz的時鐘下用時6個周期(即0.12μs)完成轉換操作。而在最常用的串口傳輸波特率9 600 b/s下,傳送1個碼元的時間為10-1ms量級。從而可以得出:完成從ASCII碼所表示的實數(-9 999.999 9~+9 999.999 9)到單精度浮點的轉換所用的時間將在10-1μs量級以下,具有較高的實時性。

4 結語

本文的實現向單精度浮點的轉換占用1 161個slice資源,在FPGA發展到今天,FPGA的容量和資源都有了很大提高的情況下,這樣的資源占用量在大多數應用中是可以承受的。本文的設計可以很容易地根據實際實數的范圍進行調整,并且可以推廣到其他浮點格式,可有效地為浮點IP核提供快速且具有高精度的數據源。