摘要:介紹了基于FPGA的四層電梯控制系統的設計。該系統采用Altera公司的CycloneⅡ系列FPGA芯片EP2C5T144作為主控制芯片,采用Verilog-HDL編程描述,實現對電梯的智能控制,經仿真驗證,完成所要求功能。該設計采用模塊化編程,升級可實現任意多層電梯系統,具有很強的適應性和實用性。

關鍵詞:電梯控制;FPGA;Verilog;控制模塊

0 引言

隨著社會的發展,電梯的使用越來越普遍,對電梯功能的要求也不斷提高,其相應控制方式也在不斷發生變化。電梯的微機化控制主要有:PLC控制、單板機控制、單片機控制、單微機控制、多微機控制和人工智能控制等。隨著專用集成電路ASIC設計技術和EDA技術的發展,可編程邏輯器件的廣泛使用,為數字系統設計帶來了革命性的變化,改變了傳統的電路設計中使用的芯片多、電路復雜、出現問題不易查找、不易進行功能擴展的缺點。本設計使用FPGA器件作為主控制芯片,采用Verilog-HDL語言設計一個四樓層單個載客箱的電梯控制系統,設計采用模塊化設計,便于修改和升級,可稍加改進,實現多層電梯控制。

1 電梯控制系統總體設計

1.1 設計任務及要求

設計一個四層電梯控制系統,要求如下:

(1)各層電梯內部信號:各樓層請求按鍵、開關門請求按鍵,所在樓層顯示,電梯運行狀態顯示。外部信號:上升下降請求按鍵,所在樓層顯示,電梯運行狀態顯示。

(2)能夠存儲請求信號,電梯上升(下降)過程中,根據電梯的運行狀態,首先按方向優先、循環次序響應各請求。

(3)到達請求樓層后,該層的指示燈亮,電梯門自動打開,開門指示燈亮。延時等待時間后,電梯門自動關閉(開門指示燈滅),電梯繼續運行。電梯空閑時,停在0層。

(4)具有超載報警功能。

1.2 電梯控制系統硬件結構

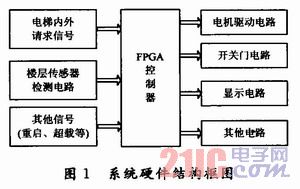

電梯控制系統硬件結構如圖1所示。

如圖1所示,該系統主要由FPGA控制器、各輸入信號模塊、輸出驅動模塊組成。FPGA控制模塊的輸入信號有:電梯內外請求信號、樓層到達信號、重啟超載報警等信號;其輸出信號分別驅動顯示電路、電梯開關門電路、電機驅動電路、以及其他如報警電路等。FPGA控制模塊是本設計的核心。

2 FPGA控制器的設計與實現

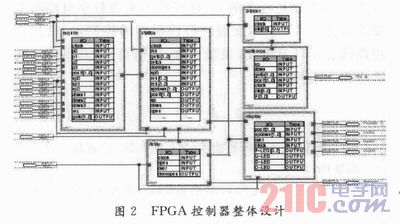

本設計的開發軟件使用Altera公司的QuartusⅡ集成開發環境,采用自上而下的設計方法,模塊設計與Verilog-HDL描述相結合的輸入方式,便于程序的維護與升級。FPGA控制器整體設計如圖2所示。

如圖2所示,FPGA控制編程主要由六個模塊組成:按鍵請求模塊、狀態控制模塊、電機驅動模塊、顯示及報警模塊、開關門控模塊、分頻模塊。各模塊的信號及功能如下:

模塊1:按鍵請求模塊

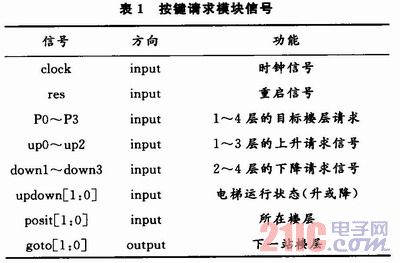

該模塊的接口信號如表1所示,模塊功能如下:

(1)利用鎖存器對輸入的請求信號進行存儲,當請求滿足后清0。為了數據表示方便,本設計的后綴0~3分別表示1~4層。

(2)根據電梯的運行狀態,按照方向優先、循環執行的原則,在請求信號中提取電梯下一站的樓層信號并輸出。如目前樓層為2層,狀態為升,那么判斷優先級為:p2/up2→p3/down3→down2→downl→p0/up0。

(3)當無請求信號時,下一站樓層為0。

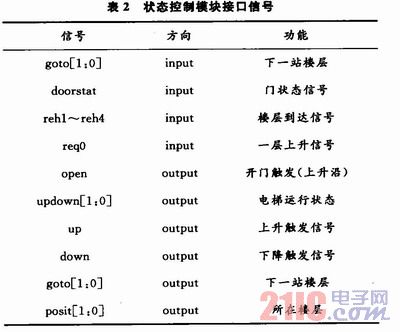

模塊2:狀態控制模塊

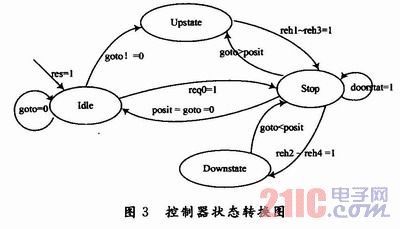

本模塊是系統設計的核心控制模塊。本文把電梯運行劃分為4個狀態,分別為:上升、下降、停止、空閑。控制系統的狀態轉換圖如圖3所示。

系統重啟時(res=1),進入空閑狀態(Idle),空閑狀態下,輸出信號posit=up=down=open=0,當輸入信號goto為0時,保持空閑狀態;當goto信號不為0時,進入上升狀態(Stop)。當第一層上升信號觸發時,進入停止狀態。停止狀態下,open信號上升沿觸發電梯開門;up=down =0,posit=goto。在電梯開門延時期間(dooropen=1),保持停止狀態;當電梯門關上時(dooropen=0),判斷下一站樓層,若大于目前樓層,進入上升狀態,若小于目前樓層,進入下降狀態。上升狀態下,up=1,updown=01,posit=goto,觸發電機控制模塊拖拽電機上升。樓層達到信號,使系統進入停止狀態。下降狀態同理。本模塊接口信號如表2所示。

模塊3:電機控制模塊

本模塊輸入信號有:上升觸發信號(up)、下降觸發信號(down)、所在樓層(posit)以及下一站樓層(goto),輸出信號:4個位不同相位的電機驅動信號。模塊由升降信號觸發,經電機狀態控制器,產生4個相位的電機驅動信號P[3:0],輸出至電機驅動電路,其頻率決定電機轉動,其相位決定電機的轉動方向。P[3:0]的各頻率信號由分頻器模塊提供。

模塊4:顯示模塊

本模塊功能用于電梯所在樓層(posit)、電梯運行狀態(updown)的七段碼顯示或LED顯示。以及超載信號(over)的報警和顯示。

模塊5:門控模塊

本模塊用來控制電梯門狀態,由輸入門控信號open信號觸發開門(doorstat=1),經過延時,電梯門自動閉合(doorstat=0)。所超載(over=1),則電梯門不合,電梯保持開門狀態,直到超載信號清除。

模塊6:分頻模塊

分頻模塊用來對系統時鐘信號分頻,產生向電機控制模塊提供的各頻率信號。

3 仿真驗證

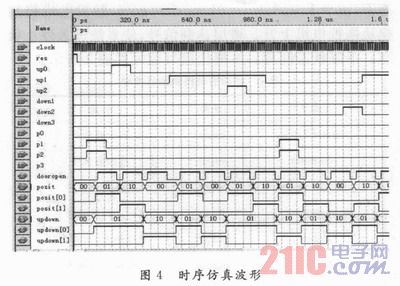

本設計頂層采用模塊化設計,各模塊采用VerilogHDL硬件描述語言。自頂向下的設計方式,便于程序查錯、升級、改進,本設計稍加修改,即可實現任意樓層電梯控制。對所設計程序進行分析、編譯、綜合、布線后產生的電路進行功能仿真和時序仿真,均可獲得符合設計要求的邏輯值。時序仿真波形如圖4所示。

由圖4可以看出:控制器始終能有效存儲各樓層請求信號,能按照方向優先、循環次序執行各樓層請求。各信號狀態符合設計要求。信號延時為10 ns級,在允許范圍內。

本設計硬件實現采用康芯KX_7CH最小系統版。程序經引腳鎖定并編程下載到器件,經測試,邏輯完全正確,達到設計要求。

4 結論

基于FPGA的數字電路設計方式在可靠性、體積、成本上的優勢是巨大的,它已經成為實現數字電路的主要手段之一。本文設計的四層電梯控制器,稍加改進即適合于任意樓層,靈活性強,運行可靠,具有很強的適應性和實用性。