ADI公司的DSP器件(ADSP-TS101)具有浮點實時處理能力強、并行性好等優點,從而廣泛被彈載信號處理系統選用。其作為彈載主處理器,在導彈的系統試驗中,需要利用上位機對其中的大數據量的軟件變量進行實時監控和記錄,這就需要一個上行傳輸給上位機的高速通信接口,數據上行的數據率需要大于6 MB/s。同時這個通信接口還需具有雙向特性,通過數據下行可實現在線程序加載與燒寫。這樣的通信接口,還需具備設備連接簡單、通用性強等特性,并能實現遠程(大于3m)數據傳輸。

ADSP-TS101自身的外總線接口和鏈路口(Linkport接口),雖速度很快,但連接復雜,難以長線傳輸,并不具備上述需求特征。可以通過在DSP的Linkport總線接口上增加FPGA實現的適配電路,擴展USB 2.0接口,實現上述應用需求。下文將介紹具體的實現方案。

1 系統總體方案

系統實現的總體方案如圖1所示。

在本方案中,USB接口芯片選用Cypress公司的CY7C68013A。該芯片是Cypress公司FX2系列USB 2.0集成微控制器之一。集成了USB 2.0收發器、SIE、增強8051微控制器和GPIF,是一種優秀的高速USB外設控制器。內置的8051微控制器獨立于USB數據通道,由SIE實現大部分USB 1.1和USB 2.0協議;USB FIFO和外部從FIFO映射到相同的8個512 B RAM模塊,實現內部傳輸和外部傳輸的無縫連接,可以較低的代價獲得較高的帶寬;8.5 KB內部RAM空間,可運行較為復雜的固件,實現軟件對硬件的配置。GPIF是由用戶可編程有限狀態機驅動的柔性8/16位并行口,可編程GPIF向量組成一個GPIF波形,匹配受控接口的時序。

ADSP-TS101作為彈載主DSP芯片,含4個鏈路口,每個鏈路口可在時鐘雙沿以8位進行雙向數據傳輸,速率高達250 MB/s。通過該接口,DSP每個處理幀將預觀測的變量結果以DMA的方式打包向上位機發送。

FPGA實現ADSP-TS101的Linkport接口與CY7C68013A之間的雙向數據緩沖和接口協議轉換。考慮到CY7C68013A中的FIFO容量較DSP的一個處理幀預發送或接收的數據量較小,故在FPGA中設置上行和下行各一個大容量FIFO,用于數據緩沖,以減少對DSP中并行流水運行的程序的打擾。這里,由于DSP鏈路口的瞬時數據率遠高于USB芯片的傳輸速率(理論上限為60 MB/s),故FIFO的DSP端口的數據傳輸為:一個處理幀只操作一次,而USB芯片端則分成多次操作。

限于篇幅,下文將重點對傳輸數據率要求高、設計難度大的上行通道的設計進行詳細描述。

2 FPGA的模擬Linkport口設計

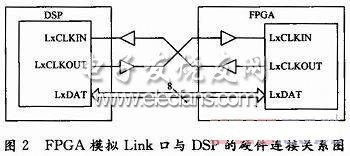

FPGA需要模擬Linkport口的接口時序,其與DSP的硬件連接關系圖如圖2所示。

Link協議通過8位并行數據總線完成雙向數據傳輸,與數據總線配合的還有相應的時鐘信號線LxCLKIN,LxCLKOUT。

2.1 Linkport口的傳輸協議

Linkport口傳輸數據時,每8個周期傳送一個4字組(16 B),在時鐘的上升沿和下降沿均傳送一個字節。在傳送過程中,發送端將檢測接收端的LxCLKOUT信號,僅當接收端將它的LxCLKOUT置為高時,即接收端處于接收方式,且有空閑的緩沖時,發送端才可以啟動下一個傳送過程。

傳送啟動過程如圖3所示,發送端驅動信號LxCLKOUT為低電平,以此向接收端發出令牌請求,發出令牌請求后,發送端等待6個周期,并驗證LxCLKIN是否依舊為高,若是則啟動傳送過程。傳送過程啟動一個周期以后,接收端將發送端的LxCLKIN驅動為低,以此作為連接測試。若接收完當前4字組后接收端無法再接收另外的4字組,則接收端保持LxCLKIN為低。這種情況下,緩沖空閑后LxCLKIN信號被禁止。若緩沖為空,則接收端將置LxCLKIN為高電平。

作為同步信號,LxCLKOUT信號由發送端驅動。數據在LxCLKOUT的上升沿和下降沿處鎖存到接收緩沖中,發送和接收緩沖都是128b寬。 LxCLKIN信號由接收端驅動,發往發送端,它通常用作“等待”指示信號,但LxCLKIN信號也可以用作連接測試信號,保證接收端能正確地接收當前傳送數據。

當LxCLKIN信號用于等待指示信號時,接收端驅動LxCLKIN信號為低電平。若LxCLKIN信號保持低電平狀態,則發送端可以[完成當前的4字組傳送,但無法啟動下一個垂字組傳送。若還有其余的數據需要傳送,發送端需將LxCLKOUT置低,并等待接收端將LxCLKIN驅動為高電平。如果在第12個時鐘沿到來之前LxCLKIN變為高電平,則緊跟著傳送的將是新的4字組。

2.2 FPGA內的Linkport口邏輯設計

由于Link協議采用雙時鐘沿傳輸數據,而同步FPGA系統中,一般只采用單一時鐘的上升沿完成操作,因此需要將FPGA系統工作頻率SCLK設定為Link時鐘的2倍。然后將該時鐘的兩分頻輸出作為LxCLKOUT信號,有效數據則在SCLK的上升沿更新。

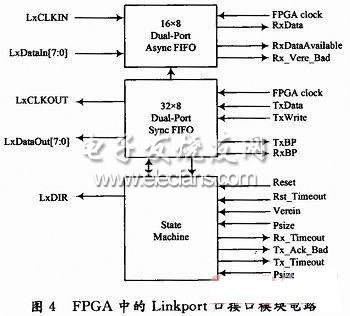

FPGA中的Linkport口接口模塊電路與ADSP-TS101的Linkport口完全兼容,且采用了雙向雙倍數據傳輸DDR技術,能實現雙向雙倍的數據傳輸。FPGA中的Link口接口模塊電路如圖4所示。

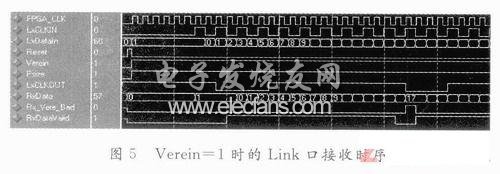

圖5是FPGA內實現DSP數據上行的Linkport口接收時序仿真圖(基于Modelsim仿真軟件)。

Link口協議的一大特點就是在收發數據時可以選擇是否需要校驗位VERE比特,VERE的啟用或關閉可以通過ADSP-TS101中的寄存器來設置,也可以通過FPGA模塊中的Verein信號置高或置低來設置。該設計在FPGA中設置VERE信號的啟用或關閉。當VERE啟用后,FPGA模塊中的輸出信號Rx_Vere_Bad用于表征最后接收的128 b數據是否正確。由于使用VERE有兩個好處,一是能保證數據的完整性;二是能減小在兩個時鐘不嚴格一致的系統中傳輸數據時產生數據重疊的可能性。因而在設計中采用了帶數據校驗的傳輸方式。3 USB傳輸設計

3.1 傳輸方式的確定

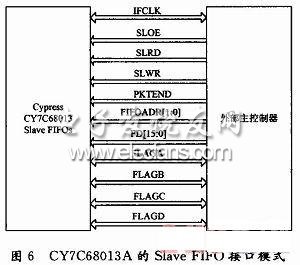

CY7C68013A芯片具有GPIF模式和從屬FIFO(Slave FIFO)模式兩種接口工作模式。在本設計中,USB數據傳輸存儲模塊負責完成存儲算法產生的大量數據的高速傳輸,由于不涉及到對外部電路的控制,所以不選用GPIF模式,而選擇Slave FIFO模式進行連接。在數據傳輸時,用Slave FIFO接口模式,批量傳輸,自動輸入(AUTOIN)方式,使用EP6端口作為上行輸入緩沖區。CY7C68013A的,Slave FIFO接口模式如圖6所示。

3.2 EZ-USB FX2時序設計

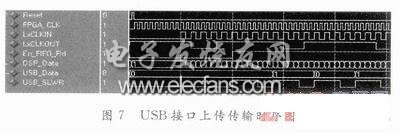

在本設計的FPGA中,設計了如圖6的外部主控制器的功能邏輯。由于DSP端Linkport口數據傳輸速率很高,而在USB端的速率可能無法跟Linkport口的數據率相匹配,故在FPGA中開辟一個2KB的FIFO,經由Linkport上傳的數據首先傳送到FIFO中,之后再經由USB口上傳至主機。為了保證數據傳輸的完整性,設計USB的數據傳輸速率為DSP Link口的1/8。在此,對FPGA邏輯應用Modelsim軟件進行了仿真,仿真結果如圖7所示。

圖7中,在LxCLKIN時鐘的上升沿和下降沿將DSP_Data中的數據寫入到FPGA的FIFO中,然后再把FIFO中的數據從數據線USB_Data中輸出給EZ-USB FX2的FD數據線,最后經由USB傳送給主機。圖中USB_Data的數據率明顯只有DSP_Data數據率的1/8,是符合設計要求的。

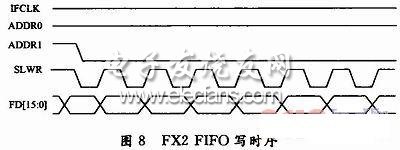

在上傳傳輸時,采用異步自動輸入方式。EZ-USB FX2芯片FIFO異步寫時序如圖8所示。根據此時序,在本設計中,FPGA輸出的USB_Data信號提供給USB的FD數據線,FPGA輸出的USB_SLWR提供給USB的SLWR,USB端便能在SLWR的下降沿把數據線FD中的數據寫入到FX2芯片FIFO中,并由USB傳送給主機。

4 結語

本文重點對DSP擴展USB接口的數據上行通道的硬件設計進行了詳細論述。本系統經測試驗證,通過該擴展USB接口,配合定制的上位機軟件,DSP數據上傳PC機的速率平均達到8 MB/s以上,連接可靠穩定,滿足對DSP變量實時監測的數據率需求,同時可通過此接口完成程序的加載與燒寫功能。僅需一臺帶USB接口的PC機,就能完成彈載DSP系統的實時測試與在線程序加載,簡捷、通用、方便,具有顯著的工程實用價值。