本文設計了1553B總線上的網絡存儲器。整個系統基于NIOS II內核設計,利用SoPC技術將接口部分的邏輯控制全部集成于FPGA片內,系統的存儲量、結點數量均可擴展。

20世紀70年代誕生的1553B總線,是一種主從式多余度總線,對總線硬件有嚴格的規定,可靠性和實時性好,已經成為當今軍用電子總線的首選。類似于以太網,1553B組網中也有“網絡硬盤”這樣的存儲需求,來減輕本地的存儲壓力,并可作為數據中繼供其他部分甚至其他組網使用。

Nios II嵌入式處理器是Altera公司于2004年6月推出的第二代用于可編程邏輯器件的可配置的軟核處理器,性能超過200 DMIPS。Nios II是基于哈佛結構的RISC通用嵌入式處理器軟核,能與用戶邏輯相結合,編程至Altera的FPGA中。處理器具有32位指令集,32位數據通道和可配置的指令以及數據緩沖。它特別為可編程邏輯進行了優化設計,也為可編程單芯片系統(SoPC)設計了一套綜合解決方案。

系統總體方案

本系統的主要功能為接收1553B網絡發來的命令、數據,管理后級存儲器,提供一個訪問存儲器的網絡接口。系統的存儲器接口作為1553B總線中的從結點,平時處于待機狀態,當總線上有讀寫命令發來時,總線轉換接口根據命令從后級存儲器讀取數據或向其寫入數據。對于總線協議,最方便的是使用現成的協議芯片,但這樣做的成本非常高,1553B協議芯片的單片價格在6000元以上,這對于普通應用來說是一個不小的負擔,如果能使用FPGA進行協議管理,將使成本大大降低,另外,Quartus內包含有很多存儲器管理的IP核可供使用,對于1553B的協議則需要自行定制組件。

系統程序為兩部分,一部分為接受網絡命令及數據,另一部分為存儲器的讀寫。在NIOS IDE環境中,使用C語言作為編程語言。

系統硬件設計

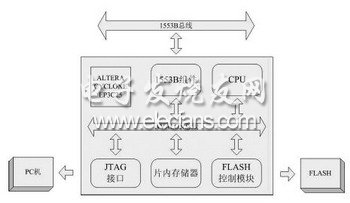

系統的硬件模塊框圖見圖1所示。

圖1 系統硬件結構框圖

系統的核心芯片采用Altera公司的CYCLONE III系列FPGA EP3C25F324。它采用了65nm低功耗工藝技術進行生產,其集成度及性能有了明顯地提高,但功耗卻非常低,加上CYCLONE系列一直定位于低成本器件,芯片整體的性價比很高。

通過Quartus II 7.2集成的SOPC軟件向FPGA內部移植Nios II內核,所需組件如下。

CPU:選用標準型CPU核,Debugger為Level 1,在滿足需求的情況下盡量節約片內資源的使用。

System_ID:下載時系統認證時使用。

Jtag_uart:FPGA與PC的通信接口,NIOS IDE軟件中使用會很方便。

onchip_memory:片內存儲器,中轉數據時使用。

FLASH:Quartus軟件內部集成有Intel公司生產的128P308的控制組件,便于開發,若需要更大量的存儲,加大FLASH容量即可,如果有需要,可多掛幾片。

FLASH_Bus:FLASH的數據是三態的,需要在CPU和FLASH之間加入Avalon三態總線橋。

1553B接口組件:與外部1553B總線通信的接口,Quartus軟件內部未集成有該組件,需要自行開發。

在1553B的網絡上,本系統是作為從結點設計的。在系統內部,1553B的接口組件需要作為Alavon總線上的主端口,其余存儲器控制模塊作為從端口。由于其余的端口在Quartus軟件內部均有集成,所以,系統軟件設計的主要工作量就是1553B接口的組件開發。

存儲芯片采用Intel公司生產的128P308的FLASH芯片,符合通用接口標準,便于后續功能容量的更新升級。

系統軟件設計

定制1553B組件的核心任務就是將1553B的總線信號轉換到NIOS II內部的Avalon總線上。

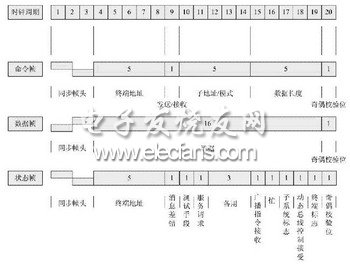

1553B組件作為Avalon總線上的主端口,選用的信號有clk、address、read、write、data、irq、reset、irqnumber等。傳輸方式為基本的主端口讀傳輸和寫傳輸。產生這些信號就需要從1553B總線上讀取的幀信號來實現。1553B總線上共有三種幀,命令幀、狀態幀和數據幀。這三種幀的結構如圖2所示。

圖2 1553B總線的三種幀結構

對于這三種幀,命令幀、數據幀和狀態幀可以使用同一個緩存,因為作為存儲的從結點不會主動向主結點發送數據,整個工作都是被動接收主結點的命令,等待主結點讀取或寫入數據,系統只有單一的狀態,不會出現沖突。

對于Avalon總線中的信號,對應于幀內信號關系如下。

read/write信號:命令幀內的發送/接收位。

address信號:命令幀內的子地址以及數據長度位。

data信號:數據幀內的數據位。

irq信號:狀態幀內的標志位引起。

irqnumber信號:狀態幀內的具體位置。

1553B組件的API函數包括有:

altera_avalon_1553B_init()

altera_avalon_1553B_enable()

altera_avalon_1553B_disable()

altera_avalon_1553B_getframe()

altera_avalon_1553B_sendframe()

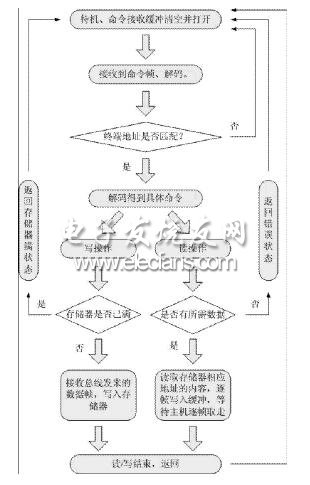

其余定制組件的步驟不再贅述。將組件通過SoPC定義完成后,命名為1553B,添加至NIOS II內核中。FPGA內部的工作流程如圖3所示。

圖3 FPGA內部工作流程

系統平時處于待機狀態,當命令幀到來時會引起中斷,中斷子程即通過altera_avalon_1553B_getframe()解讀命令幀的內容,確定是讀取還是寫入,讀取或寫入數據的長度,數據的特征作為下次讀取的標志,確實無誤后,開始讀取或寫入。

存儲器的管理與其他應用中不同的有兩點:在每次寫入后,必須將寫入的數據作一個標志,以方便以后讀取;另外,還要計算剩余存儲的容量,在下一次需要寫入數據時判斷是否可以容納下本次存儲。1553B的主結點在使用完畢數據后也需要提供信號來清空存儲以釋放資源。