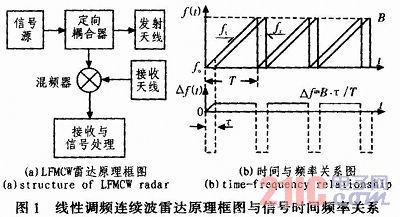

1 線性調(diào)頻連續(xù)波雷達(dá)系統(tǒng)方案

傳統(tǒng)線性調(diào)頻連續(xù)波雷達(dá)的原理結(jié)構(gòu)和時(shí)間頻率關(guān)系如圖1所示,用發(fā)射信號(hào)與接收信號(hào)進(jìn)行混頻,得到零差拍信號(hào),該信號(hào)的頻率反映了目標(biāo)的距離信息。對每一周期有效時(shí)間內(nèi)的零差拍信號(hào)進(jìn)行頻譜分析,便可提取出目標(biāo)的距離信息。

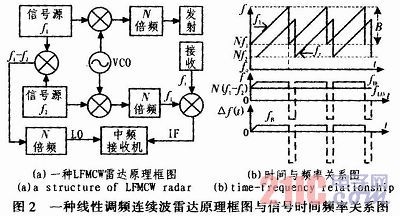

本文中中頻信號(hào)接收機(jī)所針對的一種線性調(diào)頻連續(xù)波雷達(dá)的結(jié)構(gòu)與圖1中結(jié)構(gòu)有所不同,如圖2所示。

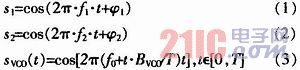

設(shè)信號(hào)源1,信號(hào)源2以及VCO的信號(hào)形式分別為:

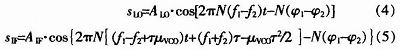

假設(shè)目標(biāo)距離為R,回波延時(shí)為τ,壓控振蕩器VCO的調(diào)頻斜率為μVCO,則易得到中頻接收機(jī)的輸入本振,中頻信號(hào)以及混頻得到基帶信號(hào)的形式分別為:

![]()

顯然NμVCOτ就是對應(yīng)的基帶信號(hào)頻率fB,N和μVCO是定值,所以提取出基帶信號(hào)頻率就可求出回波延時(shí)τ,也就得到了目標(biāo)的距離。設(shè)μ=NμVCO為雷達(dá)發(fā)射載波的調(diào)頻斜率,則易得目標(biāo)距離與基帶信號(hào)頻率之間的關(guān)系式:

![]()

在該線性調(diào)頻連續(xù)波雷達(dá)系統(tǒng)中,中頻接收機(jī)收到的本振信號(hào)是兩個(gè)固定頻率源的差頻的N倍頻,也是一個(gè)固定頻率的信號(hào),fLO=1.2 GHz,雷達(dá)發(fā)射載波的調(diào)頻斜率是VCO調(diào)頻斜率μVCO的N倍,μ=240GHz/s,線性調(diào)頻周期T=10ms。由于該雷達(dá)用于近距離高分辨率成像及隱蔽物體的檢查,作用距離較小,Rmax=100 m,將μ、Rmax以及光速c帶入式(7)中可得fBmax=160kHz,所以基帶信號(hào)的實(shí)際有用帶寬為160kHz。

2 系統(tǒng)硬/軟件設(shè)計(jì)

2.1 模擬中頻信號(hào)到數(shù)字基帶信號(hào)的處理方案

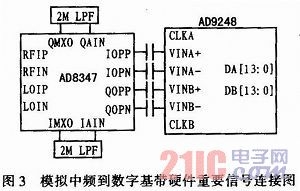

AD8347的射頻信號(hào)輸入范圍800 MHz~2.7GHz,-3dB解調(diào)帶寬為65MHz,由于輸入的中頻信號(hào)IF頻率為1.2GHz,基帶信號(hào)實(shí)際有用帶寬160 kHz,輸入輸出信號(hào)的頻帶AD8347都完全適用。AD8347的正交誤差1°,振幅平衡0.3 dB,具有較好的精度。內(nèi)部集成69.5 dB自動(dòng)增益放大器,能夠適應(yīng)-70~10 dBm輸入功率變化。

AD9248-65是一款14位雙通道,最高采樣頻率65 MSPS的模數(shù)轉(zhuǎn)換器,具有高性能采樣保持放大器、時(shí)鐘占空比穩(wěn)定器和內(nèi)部參考電壓。信噪比71.6dBc,無雜散動(dòng)態(tài)范圍80dBc,全功率輸入帶寬500 MHz,300 mW的低功率。在實(shí)際應(yīng)用中,選擇使用內(nèi)部參考電壓,輸入電壓范圍選擇2 V峰峰值。

實(shí)際有用基帶信號(hào)帶寬160kHz,在采樣之前需做抗混疊濾波,LC濾波器不易做到1MHz以下的低通,故濾波器選擇了通帶截止頻率2MHz,阻帶起始頻率5 MHz的LC低通濾波器,采樣率50 MSPS,采樣頻率為帶寬的10倍,過采樣還能提高信噪比。模擬中頻到數(shù)字基帶硬件重要信號(hào)連接圖所圖3所示。

2.2 基于FPGA的數(shù)字信號(hào)處理方案

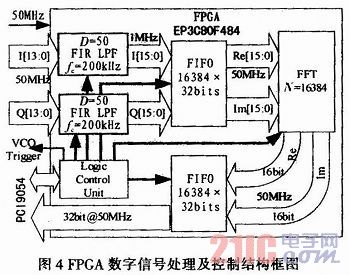

根據(jù)FPGA要實(shí)現(xiàn)的數(shù)字信號(hào)處理功能以及存儲(chǔ)容量和時(shí)序控制邏輯的規(guī)模,評估了所需要FPGA的邏輯資源、管腳數(shù)量、片內(nèi)存儲(chǔ)資源等因素,最終選取了Ahera公司Cyclone III系列的EP3CSOF484C8。FPGA系統(tǒng)時(shí)鐘50 MHz,采用主動(dòng)串行(AS)配置方式,配置芯片選擇EPCS16。

由于抗混疊濾波器的通帶截止頻率為2 MHz,相對于160 kHz的實(shí)際有用基帶信號(hào)帶寬,仍然存在很大的帶外噪聲,并且由于50 MSPS的采樣率過高,導(dǎo)致數(shù)據(jù)率大大超過了實(shí)際需求,所以在FPGA內(nèi)部首先要做1/O兩路并行的抽取式FIR低通濾波。抽取系數(shù)50,系數(shù)精度16位,輸入位寬14位,輸出保留16位。通帶截止頻率160kHz,階數(shù)為400階,Blackman窗,在400kHz處衰減80dB。抽取之后得到的實(shí)際采樣率為1MHz,是400 kHz帶寬的2.5倍,滿足奈奎斯特采樣要求。既有效濾除了絕大部分帶外噪聲,又降低了數(shù)據(jù)率。

線性調(diào)頻連續(xù)波雷達(dá)的發(fā)射與接收是需要同步進(jìn)行的,系統(tǒng)采用由接收機(jī)發(fā)出Trigger信號(hào)觸發(fā)發(fā)射機(jī)的VCO開始掃頻的方式。上位機(jī)通過PCI9054把開始指令發(fā)給FPGA,F(xiàn)PGA各模塊進(jìn)入工作狀態(tài)的同時(shí)發(fā)送Trigger信號(hào)觸發(fā)VCO開始線性調(diào)頻。

輸入的采樣數(shù)據(jù)經(jīng)FIR低通抽取濾波以后,每50個(gè)時(shí)鐘周期輸出一次,所以整個(gè)VCO掃頻周期內(nèi)得到的數(shù)據(jù)僅10 000次。由于FFT變換采用的是Altera FFT IP核的Burst數(shù)據(jù)流模式,需要將一幀源數(shù)據(jù)連續(xù)輸入,而抽取濾波器輸出的數(shù)據(jù)流是非連續(xù)的,所以采用了16384x32bits的FIFO1進(jìn)行緩存,VCO掃頻結(jié)束后,再將FIFO1中的數(shù)據(jù)連續(xù)地傳輸給16384點(diǎn)的FFT運(yùn)算模塊,有效數(shù)據(jù)僅有10000點(diǎn),需添6384點(diǎn)零補(bǔ)齊。

FFT變換輸出的實(shí)部和虛部數(shù)據(jù)各16位,每幀16 384點(diǎn),存入16 384x32 bits的異步FIFO2,F(xiàn)IFO2可以完整存放一幀數(shù)據(jù)。當(dāng)FIFO2非空時(shí),F(xiàn)PGA對PCI9054產(chǎn)生本地中斷LINT#信號(hào),PCI9054通過Local總線將FIFO2中的數(shù)據(jù)讀出。FPGA數(shù)字信號(hào)處理及控制結(jié)構(gòu)框圖如圖4所示。

2.3 PCI總線接口方案

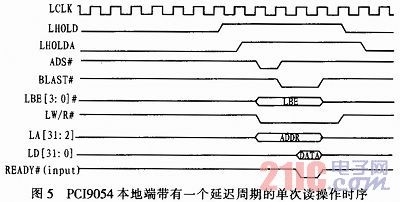

系統(tǒng)采用了PCI9054作為接口芯片,為PCI總線和局部總線建立起一條高速的數(shù)據(jù)通道,突發(fā)數(shù)據(jù)傳輸速度峰值可達(dá)132 MB/s。本系統(tǒng)中PCI9054采用本地?cái)?shù)據(jù)和地址非多路復(fù)用的C模式,數(shù)據(jù)總線寬32位,本地時(shí)鐘50 MHz。

PCI9054負(fù)責(zé)將上位機(jī)的指令通過本地總線發(fā)送給FPGA,接收到FPGA發(fā)出的LINT#中斷后對上位機(jī)產(chǎn)生INTA#中斷,上位機(jī)收到中斷后通過PCI9054讀取FPGA中FFT變換得到的數(shù)據(jù)。讀操作時(shí)序如圖5所示。

2.4 系統(tǒng)軟件設(shè)計(jì)

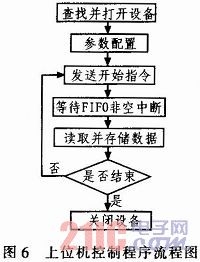

PLX公司為PCI9054提供了一套PLXSDK開發(fā)套件,其中包括驅(qū)動(dòng)程序、PLXMon調(diào)試工具以及API函數(shù),在VC++6.0中完成上位機(jī)控制臺(tái)操作界面的設(shè)計(jì)并調(diào)用API函數(shù)完成對PCI9054的操作。上位機(jī)控制程序流程圖如圖6所示。

3 實(shí)驗(yàn)結(jié)果

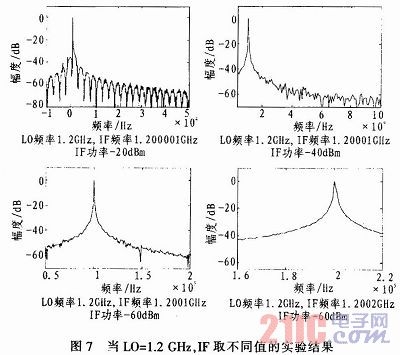

因?yàn)閷τ谝粋€(gè)距離一定的目標(biāo),其理想回波的中頻信號(hào)就是一個(gè)單頻信號(hào),所以在單獨(dú)測試中頻接收機(jī)時(shí)可以分別用兩臺(tái)信號(hào)源產(chǎn)生兩個(gè)單頻信號(hào)輸入接收機(jī)的IF和LO接收端,LO輸入信號(hào)頻率1.2 GHz,功率-10 dBm。IF信號(hào)頻率為1.2 GHz偏差在200 kHz范圍內(nèi),功率-60~10dBm。

從圖7中可以看出,當(dāng)IF頻率為1.200 001GHz,信號(hào)功率為-20dBm,得到基帶信號(hào)頻率為1kHz,信噪比約為60dB;當(dāng)IF頻率為1.200 01 GHz,信號(hào)功率為-40 dBm,得到基帶信號(hào)頻率為10 kHz,信噪比約為60dB;當(dāng)IF頻率為1.200 1 GHz,信號(hào)功率為-60 dBm,得到基帶信號(hào)頻率為100 kHz,信噪比約為50 dB,所以雖然中頻輸入信號(hào)IF的信號(hào)功率衰減到了-60 dBm,得到基帶信號(hào)的信噪比仍能保持在一個(gè)較好的結(jié)果,這是由于前段混頻器AD8347具有69.5 dB自動(dòng)增益放大器。當(dāng)IF頻率為1.200 2 GHz,信號(hào)功率為-60 dBm,與IF頻率為1.200 1 GHz時(shí)的功率相同,但得到2 kHz基帶信號(hào)的信噪比約為40 dB,說明FIR低通濾波器起了作用,在200 kHz處已經(jīng)衰減了10 dB以上。所以可以證明中頻接收機(jī)對1.2 GHz偏差1~160 kHz范圍都能良好地完成接收任務(wù),可以準(zhǔn)確地測量出IF信號(hào)與LO的差頻。

4 結(jié)論

本文闡述了一種線性調(diào)頻連續(xù)波雷達(dá)中頻接收機(jī)的系統(tǒng)結(jié)構(gòu),針對系統(tǒng)參數(shù)完成了中頻接收機(jī)的硬/軟件設(shè)計(jì),能夠?qū)崿F(xiàn)對中頻信號(hào)的接收和處理,測量目標(biāo)回波的差拍頻率,可實(shí)現(xiàn)近距離高分辨率探測,采集處理后存儲(chǔ)的數(shù)據(jù)可用于雷達(dá)成像。