在現代電子戰環境中,信號一般都具有密集化、復雜化的特點,而且占用的頻譜越來越寬,從而對寬帶數字信道化接收機準確接收信號提出了更高的要求。一般的數字接收機在監視整個頻段時,由于相鄰信道間往往會存在盲區,有可能丟失信號,而改進后的無盲區多相濾波器的信道數與抽取倍數不再相等,信道數和抽取因子之間往往存在倍數關系。FPGA以其自身的結構和高速的數據處理能力及大量的乘加器、存儲器及邏輯單元,成為一種重要的信號處理工具,在高速數字濾波器的設計方面更有其明顯的優勢。

1 數字信道化原理

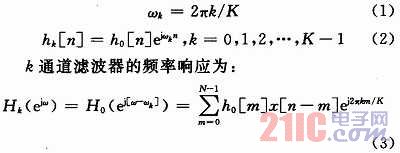

x[n]是經過A/D轉換后的輸入信號,在這個數字接收機中每個帶通濾波器都源于一個原型低通濾波器h0[n]。如果h0[n]是一個長度為N的實系數因果低通濾波器h0[n]={h[0],h[1],…,h[N-1]}。這個低通濾波器能變換成一系列帶通濾波器,第k個信道的中心頻率為:

對一般的數字接收機,原型低通濾波器的長度N大于信道數K,如果N=KP,則:

數字信道化處理后,頻率將為原來的1/M,故可以進行M倍的抽取。

![]()

數字信道化即由一個低通和若干帶通濾波器組成的濾波器組,是信道化的根本,但如果A/D的采樣信號直接送入各濾波器做數字濾波,則運算量很大,硬件上難以實現,故采用多相濾波的方法。先做抽取使信號速率降低,再進入多相濾波器組,具體流程如圖1所示。

多項濾波器的結構一般情況下為K=FM,K為總信道數;M為每路數據的抽取倍數。讓h0[n]為原型低通濾波器,該濾波器能分解成K相分量。

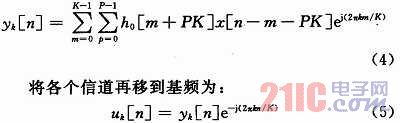

則F=2時的硬件實現框圖如圖2所示。

2 系統的Matlab仿真

首先要設計原型低通濾波器,Matlab是工程應用、信號處理、數學計算領域里非常實用的工具。根據相應的需要設計滿足一定指標的濾波器。Matlab中的firpmord是采用最佳逼近最大最小準則的算法,該函數可以求出原型低通濾波器的階數,指令firpm可以求出原型低通濾波器的系數。若采樣率fs為200MHz,將0~fs劃分為16個均勻信道,則低通濾波器的通帶截止頻率為6.25MHz,阻帶截止頻率為12.5MHz。相應的濾波器設計指標設計為通帶增益為1,阻帶增益為0,通帶紋波為0.01 dB,阻帶衰減為60 dB,采樣率為200 MHz。

根據這些參數得到96階的FIR濾波器,FIR濾波器特性如圖3所示。

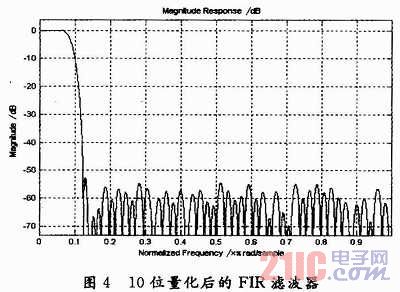

由于在FPGA中的編程需要量化后的濾波器,因此得到該FIR濾波器10位量化后的特性如圖4所示。

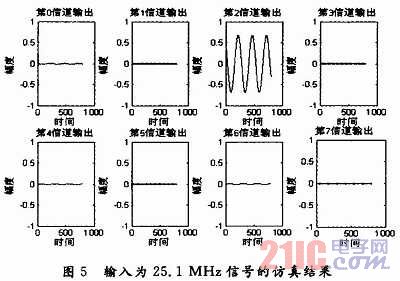

對原型低通濾波器做16倍的抽取,2倍內插得到濾波器的多相分量。在Matlab環境仿真基于多相濾波器的數字信道化過程,結果如圖5所示。

由圖5可知,25.1 MHz的信號處于第2個信道,而仿真結果也說明在第2個信道的輸出幅度最大,是其他信道輸出的60 dB以上。

3 信道化接收機硬件平臺

3.1 硬件系統

由矢量信號源(JUNG JIN SG-1710)產生0~200 MHz的信號,經過變壓器后進入A/D,輸出LVDS數據和同步時鐘給FPGA。通過壓控振蕩器,產生200MHz的差分時鐘驅動A/D。A/D轉換器選取LTC2242-10,它是Linear公司推出的10位250 MSPS,高IF采樣模/數轉換器,該器件提供1.2GHz模擬輸入帶寬,需要2.5V的工作電源。FPGA采用的是Altera公司的StratixⅡ系列的EP2S60F484,等級為C5。壓控振蕩器采用A/D公司的AD9516-3,AD9516-3提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,還配有片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。AD-9516-3提供4路LVDS輸出的工作頻率達800 MHz,在該系統中LVDS輸出200 MHz的時鐘驅動A/D。系統硬件框圖如圖6所示。

3.2 硬件系統實現

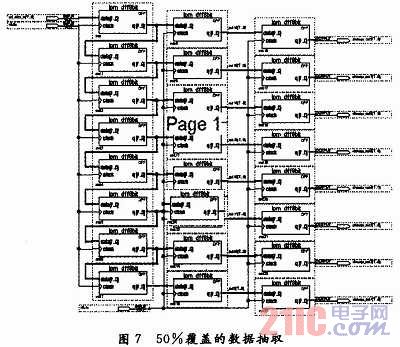

根據多項濾波器組理論和Matlab程序仿真的結果,在FPGA內部實現寬帶信號的信道化。中頻化的信號通過變壓器經AD采集后輸出差分數據。由圖2數字信道化接收機實現框圖可知,在0~200 MHz的范圍內均勻信道化成16個信道,因此需要對數據進行16/2即8倍的抽取,又由于100~200 MHz是0~100 MHz的鏡像,所以8信道是0信道的一個延遲,9信道是1信道的一個延遲,以此類推,15信道是7信道的一個延遲。所以經過抽取的數據將出現50%的覆蓋,在FPGA內部的實現方法如圖7所示。

圖7中每個單元為10位的D觸發器,第一級采用一個時鐘clk8x,第二和第三級采用時鐘clk1x,即為第一級時鐘的8分頻,時鐘的分頻和相位設置可以通過FPGA內部的PLL設置。

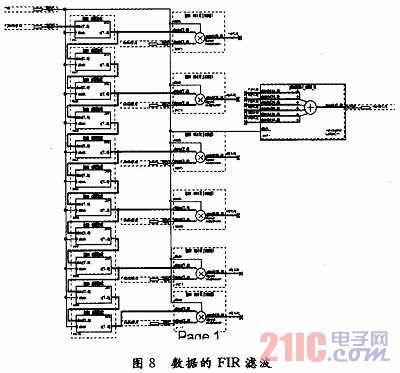

根據圖2,抽取到的數據需要濾波,根據多項濾波理論,抽取后的每個信道需要和原型低通濾波器的系數做卷積。由圖4可知該FIR濾波器的特性,根據Matlab計算得到該濾波器的96階系數,經過8倍抽取和2倍內插補0,生成16×12的矩陣。得到的矩陣的每一行作為相應信道的卷積系數,卷積的實現過程如圖8所示。

圖8中第一級的模塊為10位的D觸發器,第二級為乘法器,第三級為加法器,每一級的時鐘采用相同的時鐘。

由于多項濾波結構的特性,每個信道卷積后需要做并行的FFT計算,所以不能使用QuartusⅡ自帶的IP核FFT模塊,因為其自帶FFT模塊是串行計算的,而且最小支持64點的計算。

FFT的程序編寫由復數乘法器和D觸發器組成,這里用到16點的FFT有4級,每一級都要舍位保留一位符號位,因為無限制的保留數據位會造成FPGA的資源不夠,所以不僅需要通過計算調整舍位,還要確保精度。

圖9和圖10顯示了A/D采集到的數據和信道化后的數據。

圖9為矢量信號源發生器產生的在第0個信道上的正弦信號,顯示的是經過A/D采集后FPGA讀取到的數字信號用SignalTapⅡ顯示。

4 結論

文中給出寬帶信道化接收機在Matlab環境下的算法和精度仿真,驗證了算法的可行性。并根據軟件無線電思想搭建信道化接收機硬件平臺,實現了寬帶信號的信道化,實現了對0~100 MHz頻率范圍的中頻信號8信道的數字信道化。根據仿真結果和實際硬件測量得到的結果,表明該信道化接收機具有良好的檢測能力,也證明寬帶信道化接收機的在非協作通信中的檢測能力和應用意義。