2000年發布的USB 2.0規范,將USB接口的傳輸速度" title="傳輸速度">傳輸速度提高了40倍。傳輸速度的提升使得USB設備" title="USB設備">USB設備控制器的設計指標也隨之提高,雖然協議中對于緩沖區的設計要求并沒有本質上的改變,但是由于總線帶寬與傳輸速度的提高,各個芯片供應商均推出了自己的緩沖區設計方案。為了提高USB接口的數據存取速度,通常使用異步FIFO來設計端點緩沖區" title="端點緩沖區">端點緩沖區。這里首先簡要介紹USB中端點的概念,并給出一款異步FIFO的設計方案。然后根據USB四種傳輸類型的特點,提出基于該FIFO結構的不同類型的端點緩沖區的設計方案。特別是對于控制端點提出了一種新型的雙向異步FIFO結構,在保證控制傳輸的前提下,減小了將近1/2的電路面積。最后給出在Synopsys平臺下電路的VLSL實現結果。

1 USB協議中的端點及實施方案

1.1 USB設備的端點

USB主機和設備之間傳輸的數據是以信息包的格式來傳輸的,可分為令牌包、數據包、握手包和特殊包。在數據包中包括了主機和設備通信的數據分組。圖1是一個典型的USB數據包的格式。

PID域是為了增加USB通信的健壯性而設定的數據分組的辨識符;CRC16域是對數據分組進行CRC校驗的結果。DATA域是實際傳送的數據內容。USB設備控制器" title="設備控制器">設備控制器會將接收到的主機數據包放入指定的端點緩沖區;或者從指定的端點取出待發送的數據組裝成USB信息包發送到主機。

由此可見,所謂端點實際上是主機與設備之間通信的來源或目的,所有的傳輸都要傳送到設備的端點,或是由設備的端點發出。一系列相互獨立的端點在一起就構成了USB邏輯設備。從物理層的角度來看,端點是一塊存儲器區域,用以緩沖實際接收到或待發送的數據包。

USB協議中定義了四種傳輸類型,分別是控制傳輸、批量傳輸、中斷傳輸和同步傳輸。所有USB設備控制器都應該支持控制傳輸,其他三種傳輸方式根據不同的應用背影而用于不同類型的設備。按照傳輸類型可將端點分為控制端點、批量端點、中斷端點和同步端點。其中控制端點較為特殊,只有它可以雙向的傳輸數據,而其他端點只能傳輸單方向的數據。

1.2 使用異步FIFO設計USB端點

由于USB設備控制器的緩沖區空間是對應各個不同的端點。每個端點所對應的傳輸方式、傳輸方向也不同。通常控制端點會連接控制器的MCU單元,而其他類型的端點一般連接設備端的接口。可見USB的端點緩沖區實際上是在串行接口引擎時鐘和設備時鐘或MCU時鐘的兩個時鐘域之間傳輸數據。而使用異步FIFO來實現該結構顯然是一個不錯的選擇。

圖2是本文所采用的異步FIFO的結構框圖。該異步FIFO由一塊雙端口SRAM、寫地址/滿邏輯和讀地址/空邏輯、以及為了消除亞穩態的兩級同步電路組成。左端口在寫時鐘下進行數據的寫入操作;右端口在讀時鐘下實現數據的讀出操作。

對于異步FIFO的設計,產生準確的空滿標準是設計中的核心任務,它與FIFO是否能穩定工作息息相關。寫滿不溢出,讀空不多讀是異步FIFO空滿標志判斷的基本原則。傳統的判斷方法是另外設置一個狀態位,作為最高位,其余位作為地址位,當讀寫指針的地址位和狀態位全部吻合時,FIFO處于空狀態;當讀寫指針的地址位相同而狀態位相反,FIFO處于滿狀態。這種異步FIFO由于是通過直接比較二進制讀寫指針來判斷滿和空的,在跨時鐘傳遞時會有毛刺產生。下面將介紹一種通過直接比較格雷碼指針的方法生成FIFO的空滿信號,從而消除了毛刺,提高了電路的穩定性。

比如要設計一個深度為8的異步FIFO,需要使用3 b的格雷碼計數器對讀寫指針計數,與二進制類似,還是需要使用一個狀態位來判斷滿和空狀態。此時FIFO的格雷碼指針跳變情況如表1所示。

觀察表1可知,當讀指針為4’b0011時(二進制為4’b0010),此時比他多一個周期所對應的格雷碼為4’b1111(二進制為4’b1010)。兩者的高二位恰好相反,但低位完全相同。對比表1左右兩列可知當讀寫指針相差一個周期即FIFO滿時對應的格雷碼指針的最高兩位相反,而低位則完全相同;當兩者完全相等時對應為FIFO的空狀態。圖3給出的是在設計的FIFO的深度為8時,在Modelsim中的仿真波形。由圖3可知,當FIFO從空到滿時,對應的格雷碼寫指針為4’b1100,而同步后的讀指針為4’b0000;當從滿被讀空時,讀指針為4’b1100;由此可見仿真的FIFO的空滿信號與設計一致。

2 基于FIFO結構的優化端點設計方案

2.1 基于新型FIFO結構設計控制端點

上文已經論述過控制端點是一個雙向傳輸的端點,但是在同一時刻只能是單向的數據傳輸。該端點主要是用于USB設備的枚舉過程,主機發送一個信息包,設備負責回應一個信息包。對于該端點的設計現有的方案都是采用雙FIFO來實現雙向傳輸的。一個FIFO用以接收主機發送過來的數據包;另外一個FIFO用以向主機發送數據包。在傳輸數據包時總有一個FIFO處于空閑狀態,這樣會造成存儲器資源的浪費。為此,本文提出一種新型的異步FIFO結構,該結構使用一塊雙端口sram來實現控制端點的單工雙向傳輸,而傳統的雙FIFO結構需要兩塊SRAM用來實現雙向傳輸。由于SRAM占據了FIFO的大部分面積,在實現控制傳輸的功能下少用了一塊SRAM,可以預見最終的電路實現面積會減小將近1/2。

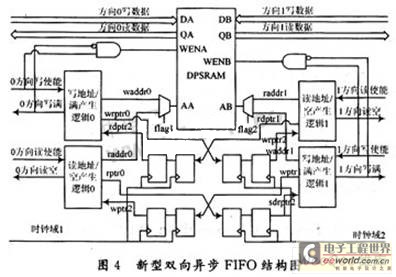

圖4是本文所設計的新型異步FIFO結構,該FIFO的實現是基于一塊雙端SRAM。在上文所提到的異步FIFO結構的基礎上增加一套讀寫指針邏輯和滿空判斷標志。這個電路可以看作是原來電路模塊的復制,即兩者設計完全一致。這兩個新增的指針模塊用以產生訪問SRAM的地址和用以產生滿和空的格雷碼指針。這樣在同一方向對于SRAM的訪問就會有兩個地址,其中一個是讀地址,另一個是寫地址。這樣需要設計一個選擇器,用以選擇當前訪問SRAM的是讀地址或寫地址。這個選擇器的選擇端可以根據不同方向的讀寫使能信號來切換。這是由于在同一時刻不可能出現一個方向的讀/寫使能均有效的現象。

對于圖4的數據路徑可簡介如下,方向0在其寫使能信號的控制下,往FIFO內寫入數據,寫滿之后方向1控制其讀使能將方向0寫入的數據讀出來。然后方向1控制其寫使能將數據寫入雙端口SRAM,方向0負責把SRAM內的數據讀出。

對于USB的控制端點,其接收的最大數據包為64 b。故本文設計的雙向FIFO使用的sram亦為64 b。使用memory complier生成。圖5是設計的雙向FIFO在Modelsim下的仿真波形圖。該波形顯示了方向0寫數據,方向1讀數據和方向1寫數據,方向0讀數據的過程。

2.2 其他端點的優化設計

對于USB設備控制器的其他端點,由于其與控制端點有所不同。控制端點是一個雙向端點,而非控制端點單向的傳輸。故對于非控制端點對應的緩沖區的容量設定,應使USB的帶寬利用率盡量達到最高。由于USB規范中規定緩沖區必須有足夠的空間,可以為全(高)速設備容納一個時間片所能傳輸的數據量的兩倍的容量。這樣USB在處理一個數據分組的同時,可以接收下一個數據分組。以此種重疊技術可以提高總線利用率。如果批量端點的緩沖區的深度設計為1 024 B。就可以得到最大的帶寬利用率。

圖6是其他端點所采用的雙緩沖FIFO方案示意圖。在狀態1,req0控制訪問FIFO0,reql控制訪問FIFO1;在狀態2,req0切換到訪問FIFO1,req1切換到訪問FIFO0。基于雙緩沖FIFO的設計方案可使其他端點的帶寬利用率達到最高,滿足高速傳輸的需求。

3 電路的ASIC實現結果

對上述設計方案采用Verilog硬件描述語言進行設計。仿真工具為Modelsim SE 6.2b,前仿真通過后,對設計好的電路使用Design Complier進行綜合。綜合所使用的工藝庫是SMIC 0.18 μm工藝庫。

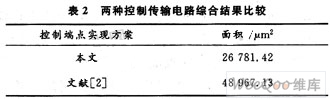

對于控制端點,考慮到其主要處在SIE時鐘和MCU時鐘之間,對其所加的時鐘約束分別為60 MHz和30 MHz;此外還對傳統的雙緩沖FIFO結構進行了綜合,兩者所加約束完全一致。將兩者的電路的綜合結果對比如表2所示。

對比表2可知在保證控制端點功能的前提下,本文所采用的新型FIFO結構比傳統雙FIFO結構在電路的實現面積方面減小了45.3%。

對于其他端點所采用的雙緩沖FIFO方案保證了傳輸速度,但卻是以犧牲面積為代價換來的。表3給出了批量(Bulk)傳輸端點(兩個深度為512 B的FIFO)的實現面積報告。

4 結 語

USB設備控制器端點緩沖區的性能,直接關系到總線的帶寬利用率。這里分析了USB的四種傳輸類型并根據其特點靈活的設計了不同的方案,并給出了最終電路的ASIC實現結果。特別是針對控制端點所提出的一種新方案具有一定的通用性,該方案可以應用在其他類似場合的設計中。